# COGNITIVE SYSTEMS RESEARCH PROGRAM

**CORNELL UNIVERSITY**

ITHACA, N. Y.

REPORT NO. 5

# SYSTEM AND CIRCUIT DESIGNS FOR THE TOBERMORY PERCEPTRON

(Preliminary Report on Phase I)

By

**GEORGE NAGY**

1 September, 1963

Prepared Under Contract No. NONR 401 (40) and NSF GP-971

### TABLE OF CONTENTS

|             | List of Figures Summary                                                                                                                                                                                                                                                                                            | Page<br>ii<br>1                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Chapter I   | The Sensory Analyzer                                                                                                                                                                                                                                                                                               | 6                                                              |

|             | 1.0 Introduction 1.1 The Input Selector 1.2 Main Audio Amplifier 1.3 Automatic Gain Control Amplifier 1.4 Volume Monitors 1.5 Audio Filters 1.6 Audio Filter Amplifier 1.7 Logarithmic Converters and Reference Supplies 1.8 Plugboard No. 1 1.9 Differential Amplifier 1.10 Sensory Delays 1.11 Trigger Generator | 6<br>9<br>11<br>21<br>21<br>35<br>7<br>41<br>44<br>46          |

| Chapter II  | The Adaptive System  2.0 Introduction  2.1 Plugboard No. 2  2.2 The A-unit  2.3 A-unit Activity Indicator  2.4 Weight Cores  2.5 100 Kcs Carrier Generator  2.6 Erase Circuit  2.7 A-unit Input Simulator                                                                                                          | 48<br>48<br>51<br>58<br>62<br>64<br>70<br>77                   |

| Chapter III | The R-unit                                                                                                                                                                                                                                                                                                         | 84                                                             |

|             | Job Introduction Job The R-unit Filter R-unit Amplifier R-unit Threshold Circuits R-unit Threshold Circuits R-unit Output Flip-Flop Reinforcement Gates Reinforcement Pulse Generator Word Termination Detector Reinforcement Timing Control                                                                       | 84<br>87<br>89<br>91<br>100<br>101<br>103<br>106<br>108<br>112 |

| Chapter IV  | Auxiliary Logic                                                                                                                                                                                                                                                                                                    | 113                                                            |

|             | 4.0 Introduction 4.1 Summary of Logic Circuits for Automatic Control (By Charles Kiessling)                                                                                                                                                                                                                        | 113                                                            |

| Chapter 5   | Power Supplies                                                                                                                                                                                                                                                                                                     | 129                                                            |

### LIST OF FIGURES

|        |        |                                             | F   | age |

|--------|--------|---------------------------------------------|-----|-----|

| Figure | 0.0.1  | Tobermory, Phase I (Four-Layer Perceptron)  |     | 3   |

|        | 0.0.2  | Tobermory, Phase I Floor Plan               |     | 4   |

|        | 0.0.3  | Isometric View of Tobermory, Phase I        |     | 5   |

|        | 1.0.1  | The Sensory Analyser                        |     | 8   |

|        | 1.1.1  | Input Selector                              |     | 10  |

|        | 1.3.1  | Amplitude Response of AGC Amplifier         |     | 14  |

|        | 1.3.2  | Frequency Response of AGC Amplifier         |     | 15  |

|        | 1.3.3  | AGC Circuit Diagram                         |     | 16  |

|        | 1.4.1  | Volume Monitor Block Diagram                |     | 18  |

|        | 1.4.2  | Filter For Audio Monitor Amplifier          |     | 19  |

| 16     | 1.4.3  | Average Amplitude Indicator                 |     | 20  |

|        | 1.5.1  | Audio Filter Circuit Diagram                |     | 23  |

|        | 1.5.2  | Pitch-Frequency Equivalence                 |     | 24  |

|        | 1.5.3  | Audio Filter Center Frequency Distribution  |     | 25  |

|        | 1.5.4  | Q Variation in Audio Inductors              |     | 26  |

|        | 1.5.5  | Component Values for Audio Filters          | 27- | 30  |

|        | 1.5.6  | Audio Filter Performance Chart              | 31- | 34  |

|        | 1.6.1  | Audio Filter Amplifier                      |     | 36  |

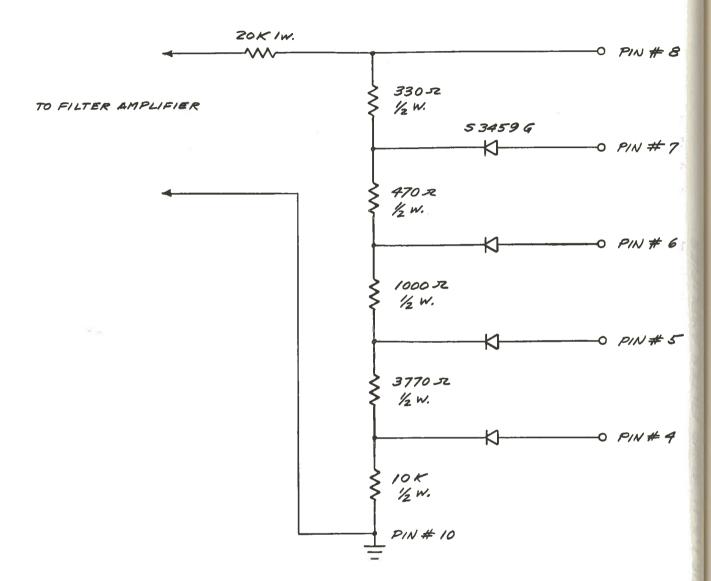

|        | 1.7.1  | Logarithmic Converter                       |     | 38  |

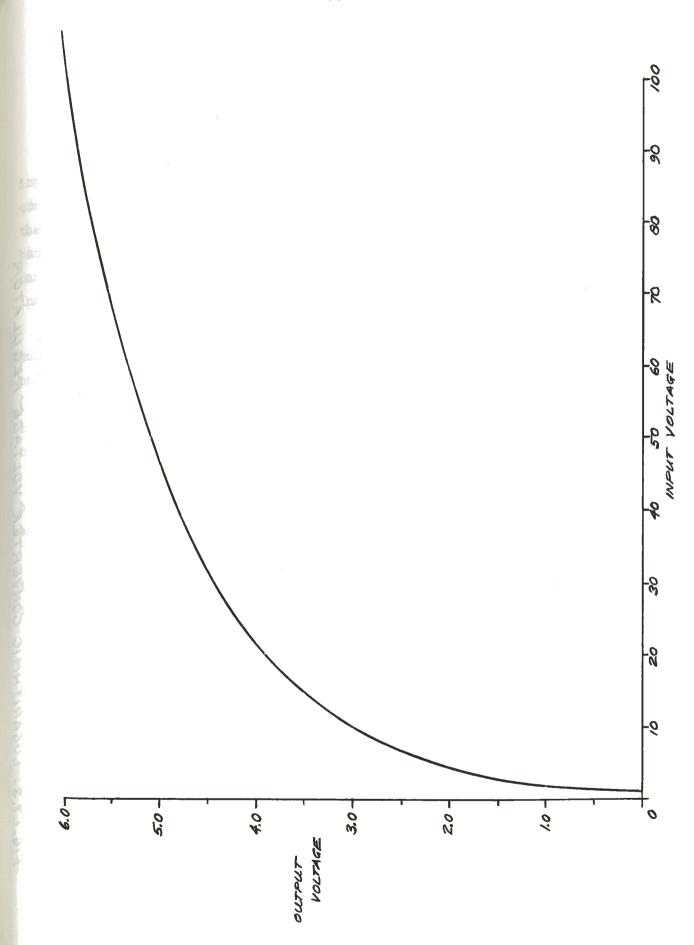

|        | 1.7.2  | Amplitude Response of Logarithmic Converter |     | 39  |

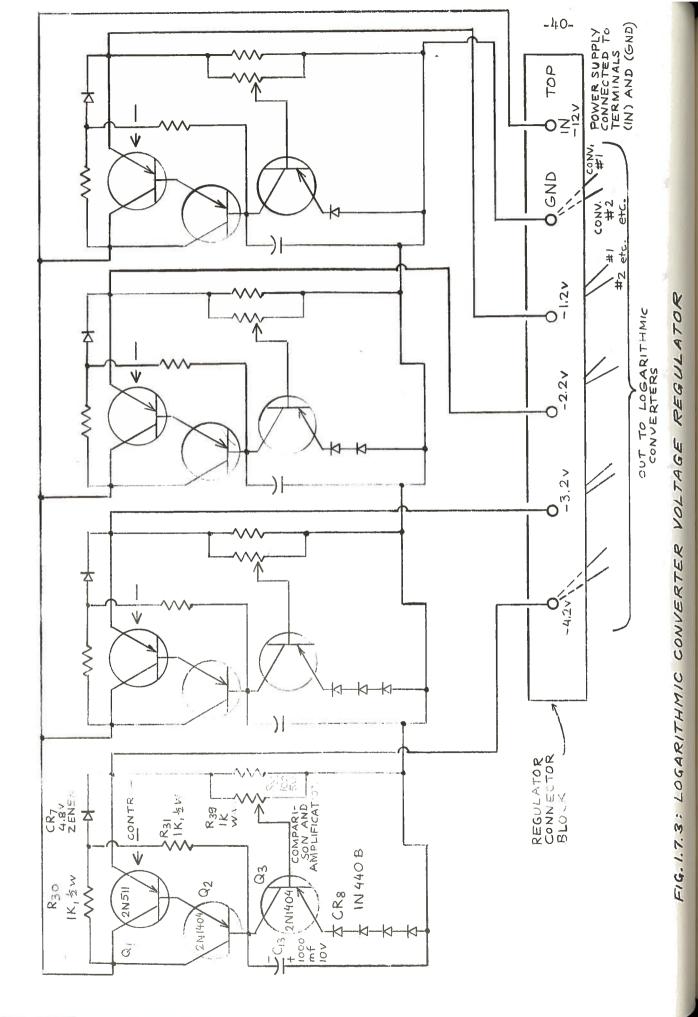

|        | 1.7.3  | Logarithmic Converter Voltage Regulator     |     | 40  |

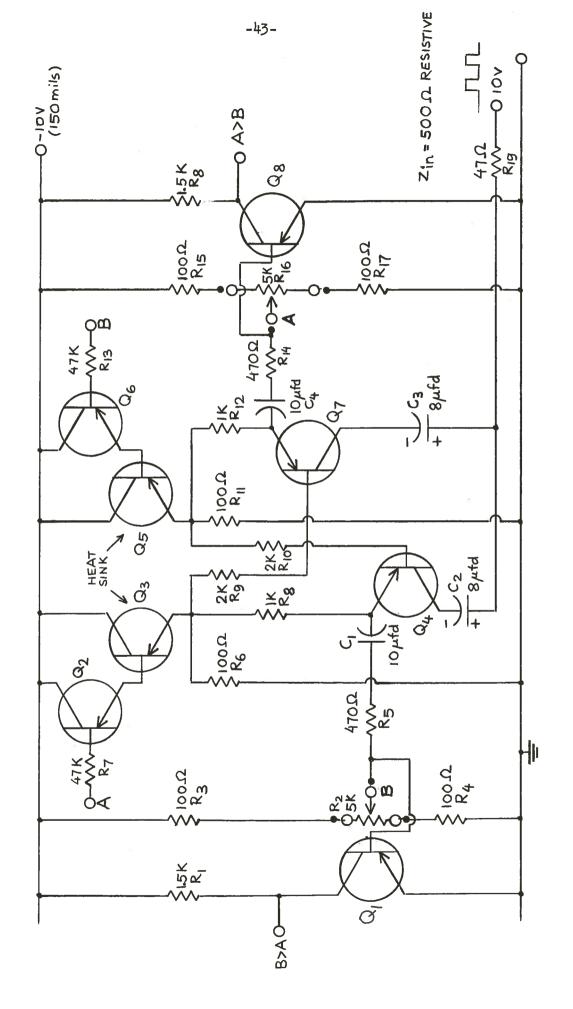

|        | 1.9.1  | Differential Amplifier                      |     | 43  |

|        | 1.10.1 | Sensory Delay Circuit Diagram               |     | 45  |

|        | 1.11.1 | Trigger Generator                           |     | 47  |

| 2.0.1 | The Adaptive System                           | 49      |

|-------|-----------------------------------------------|---------|

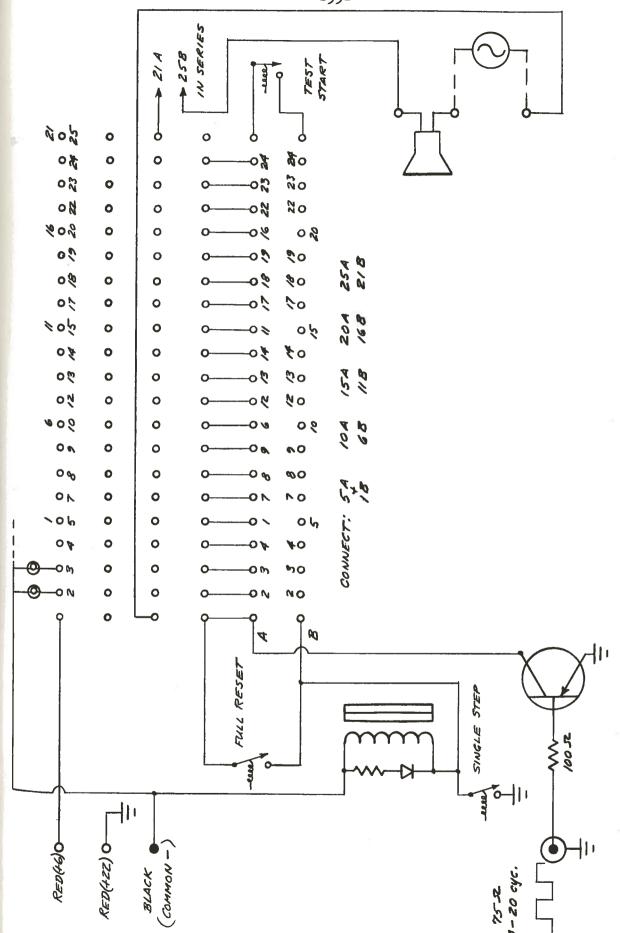

| 2.1.1 | Schematic Diagram of S-Unit Continuity Teste  | r 53    |

| 2.1.2 | Circuit Diagram of S-Unit Continuity Tester   | 55      |

| 2.1.3 | Schematic Diagram of A-Unit Continuity Tester | r 57    |

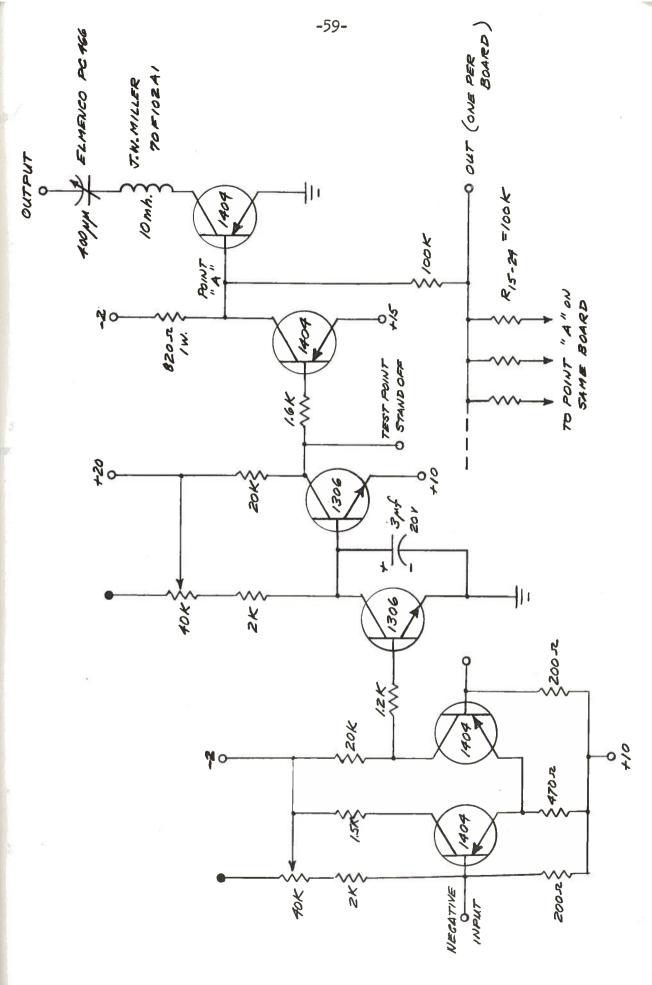

| 2.2.1 | The A-Unit                                    | 59      |

| 2.3.1 | A-Unit Activity Indicator                     | 63      |

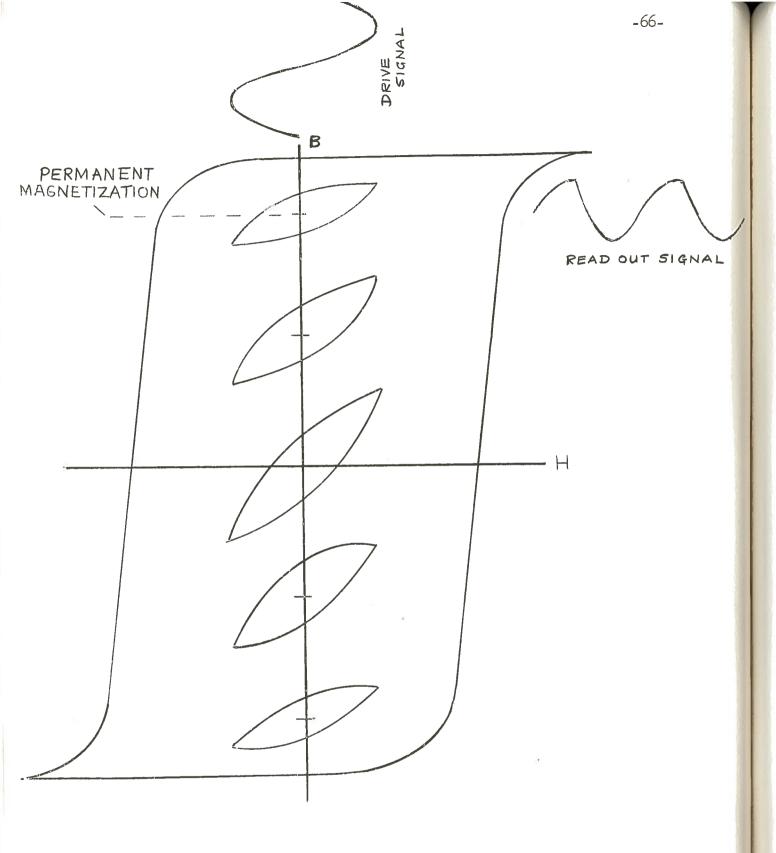

| 2.4.1 | Hysteresis Loop in Integrator Core            | 66      |

| 2.4.2 | 2nd Harmonic Memory Matrix                    | 68      |

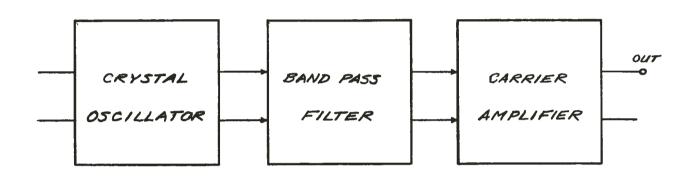

| 2.5.1 | 100 Kc/sec. Carrier Generator                 | 73      |

| 2.5.2 | 100 Kc/sec. Crystal Oscillator                | 72      |

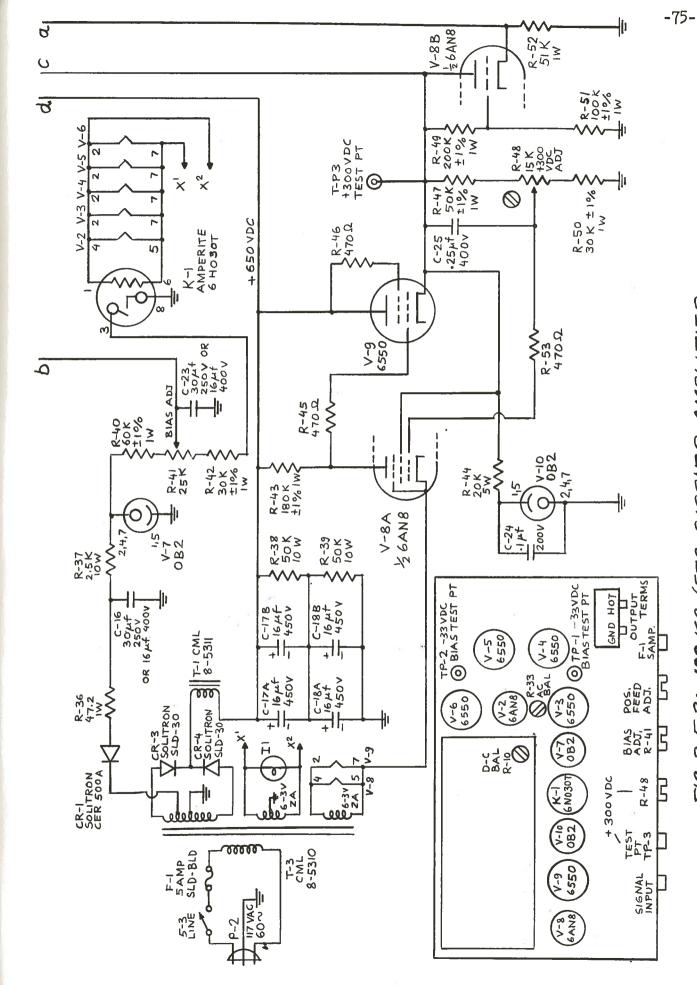

| 2.5.3 | 100 Kc/sec. Carrier Amplifier                 | 74-75   |

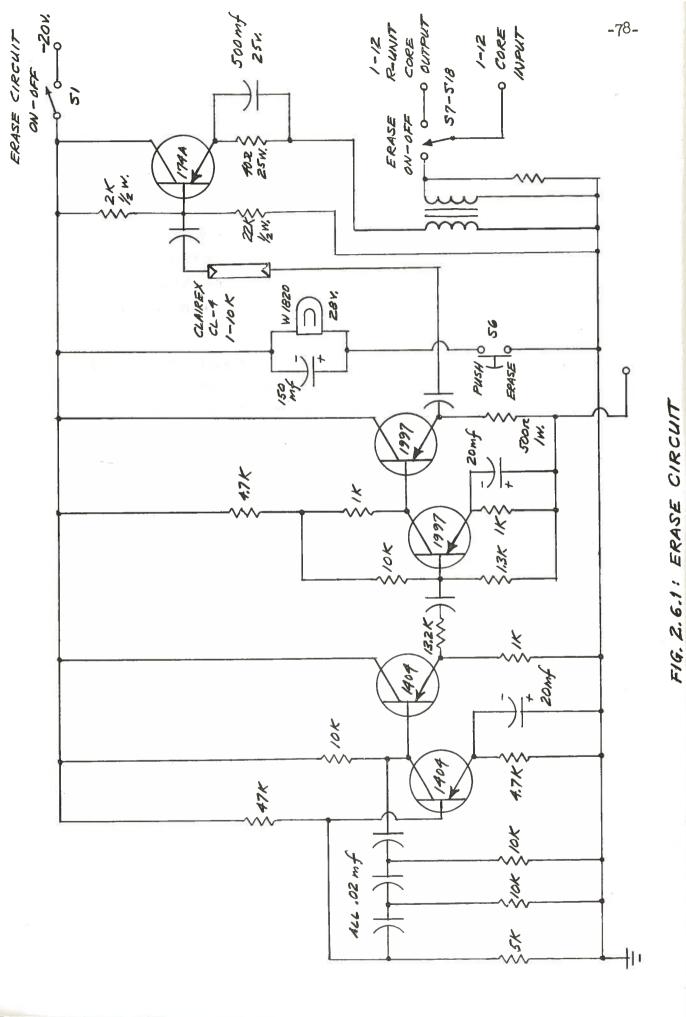

| 2.6.1 | Erase Circuit                                 | 78      |

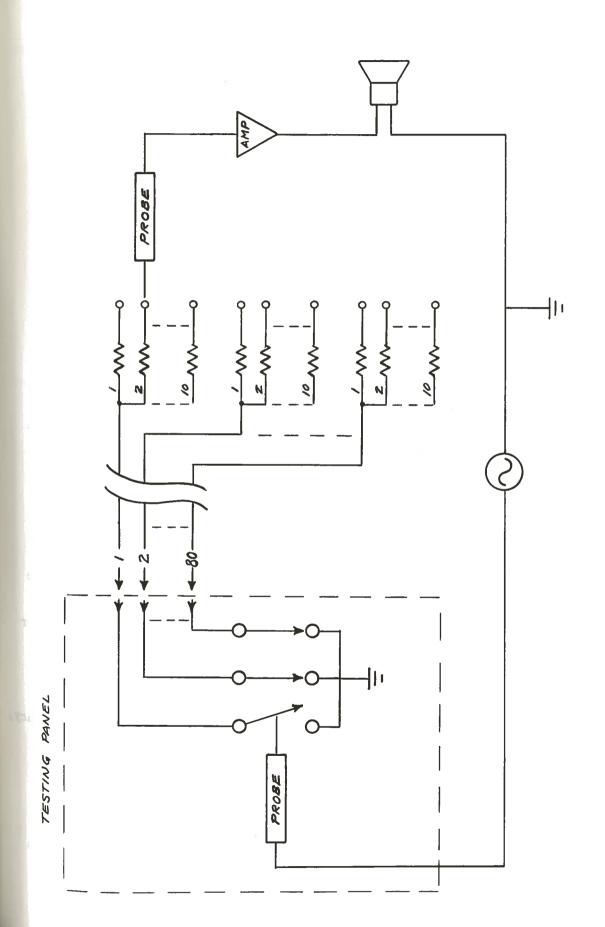

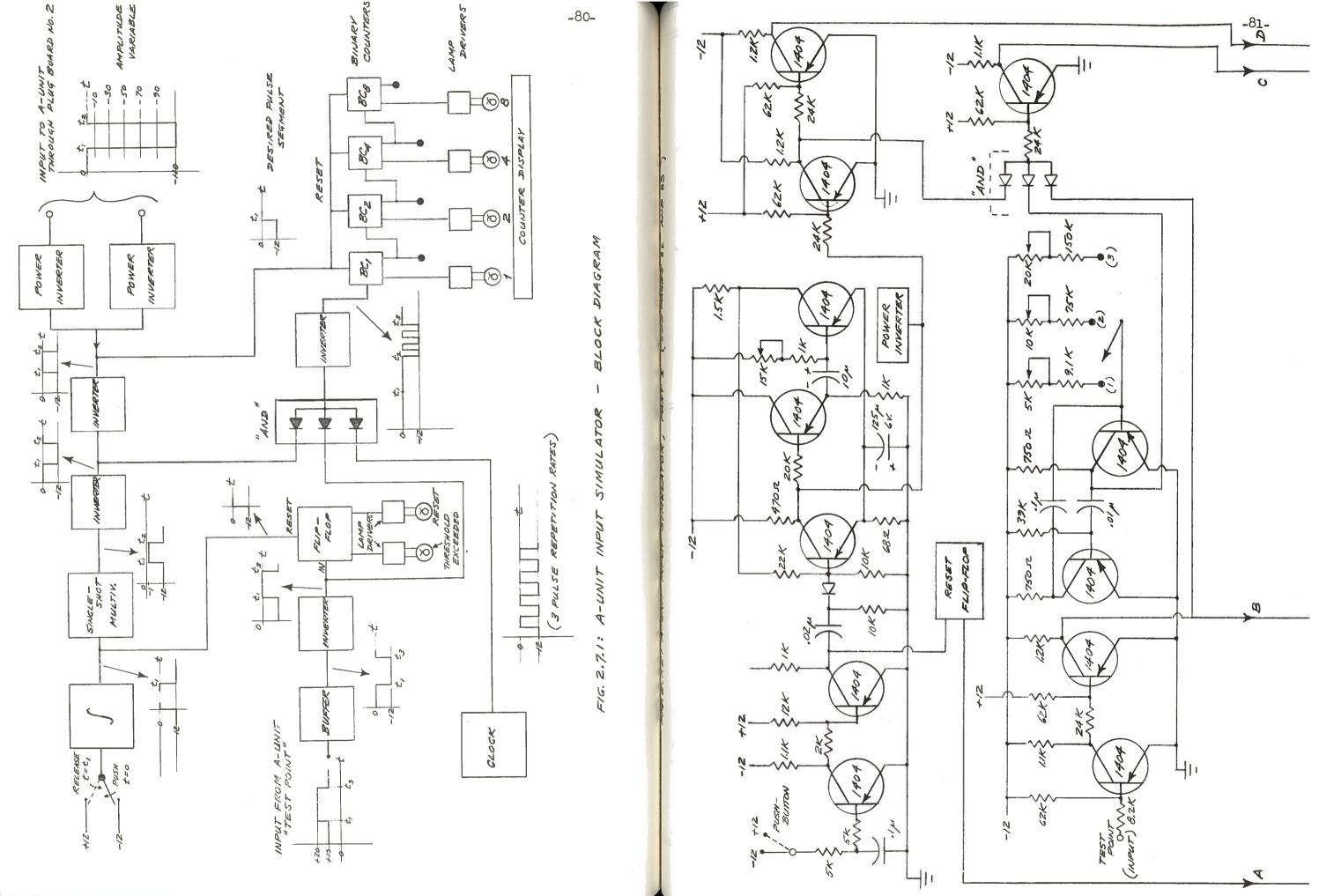

| 2.7.1 | A-Unit Input Simulator - Block Diagram        | 80      |

| 2.7.2 | A-Unit Input Simulator                        | 81-83   |

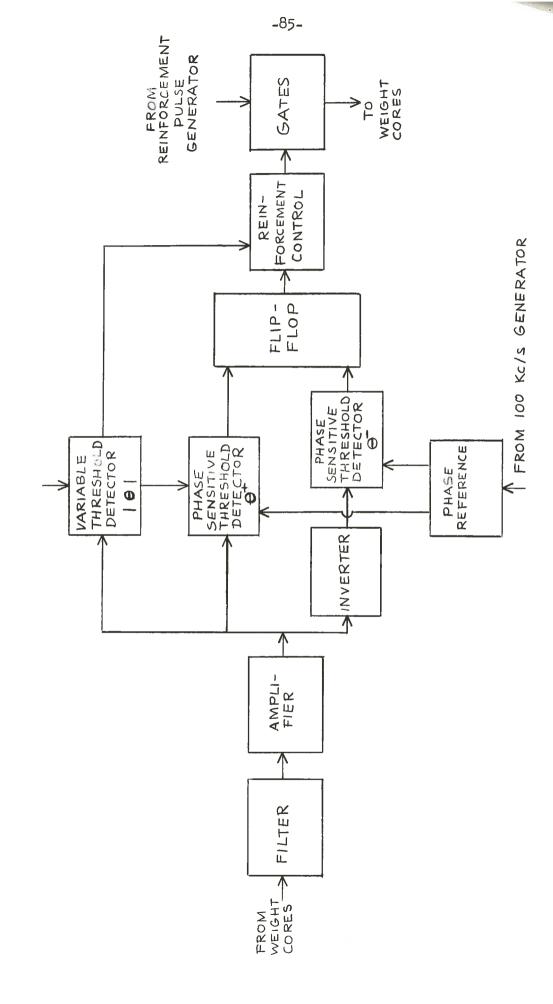

| 3.0.1 | Block Diagram of R-Unit                       | 85      |

| 3.1.1 | Filter Data Sheet                             | 88      |

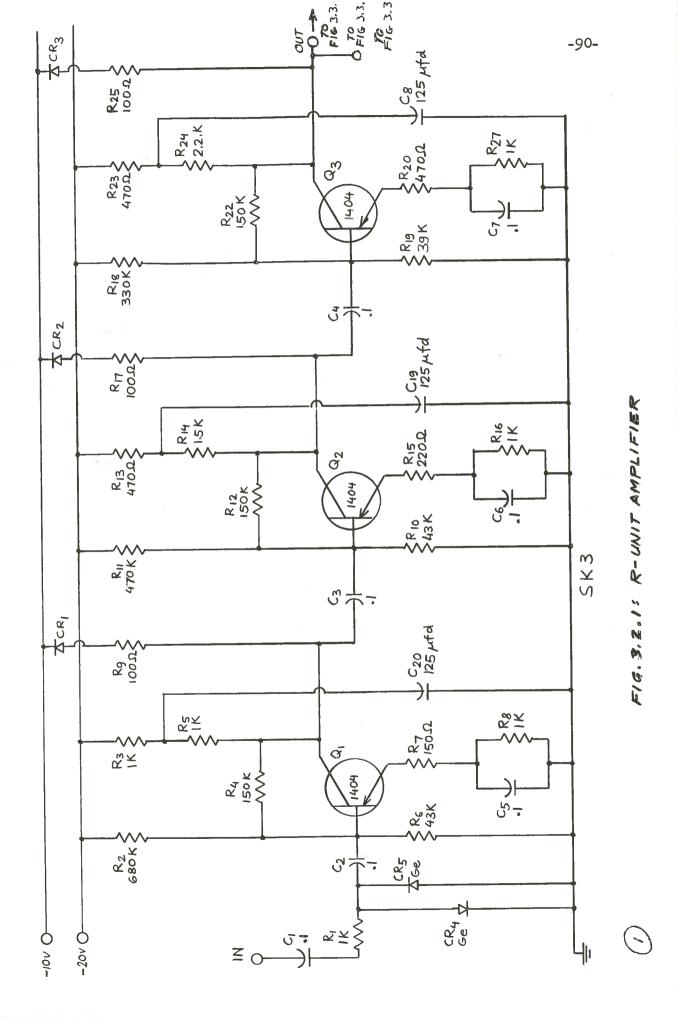

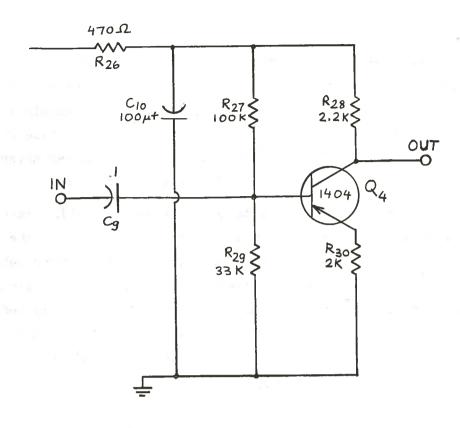

| 3.2.1 | R-Unit Amplifier                              | 90      |

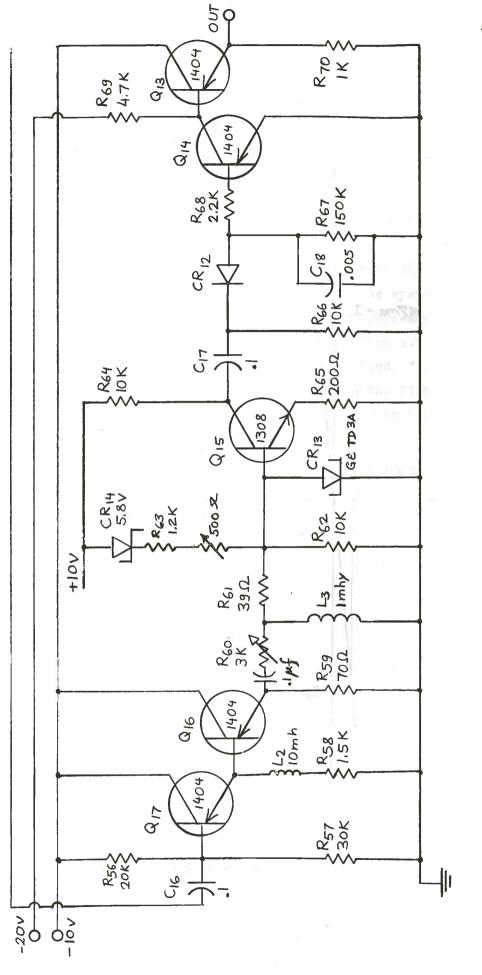

| 3.3.1 | Phase Sensitive Threshold Circuit             | 92      |

| 3.3.2 | Absolute Threshold Circuit                    | 93      |

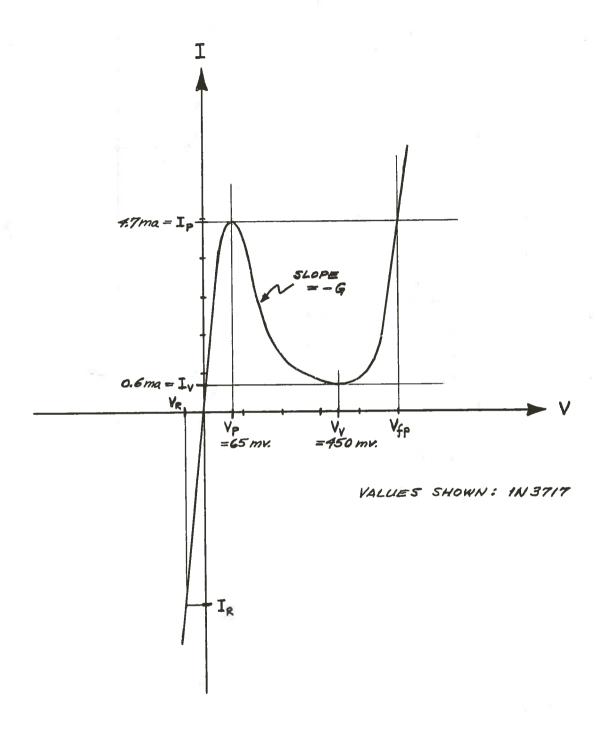

| 3.3.3 | Typical Static Characteristic-Tunnel Diode Co | urve 94 |

| 3.3.4 | Unity Gain Inverter                           | 96      |

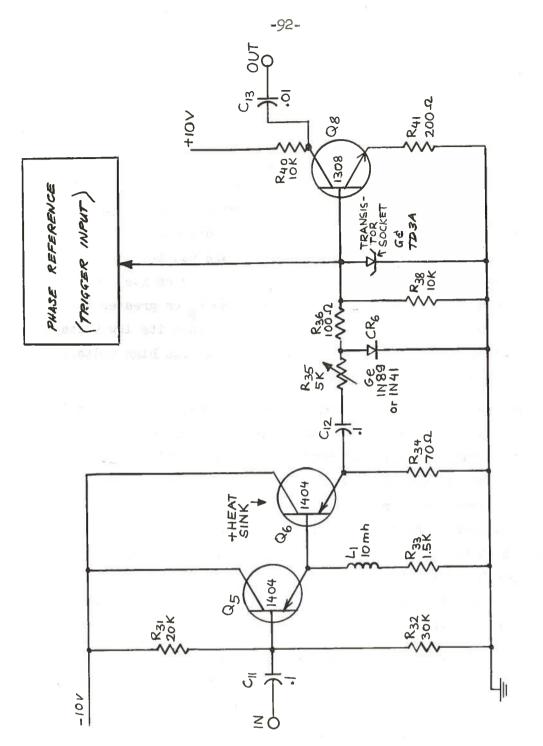

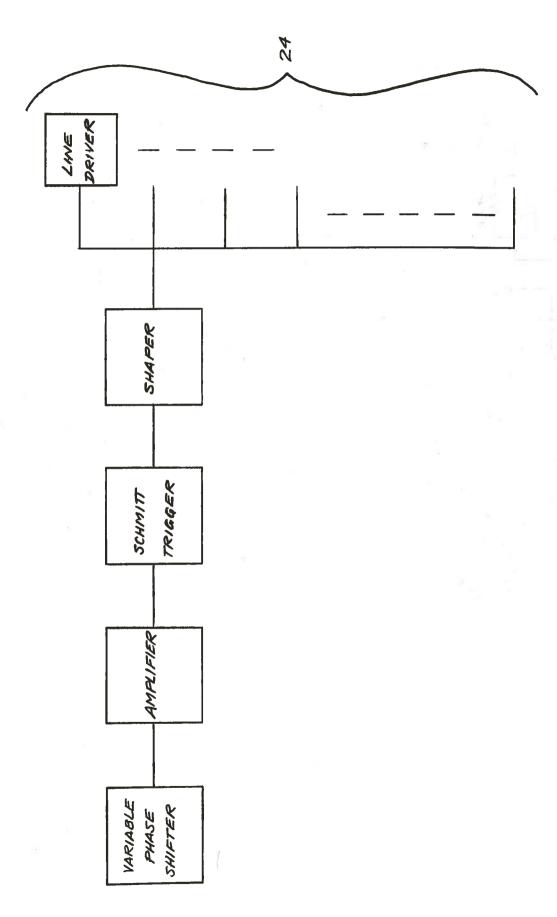

| 3.4.1 | Phase Reference Block Diagram                 | 97      |

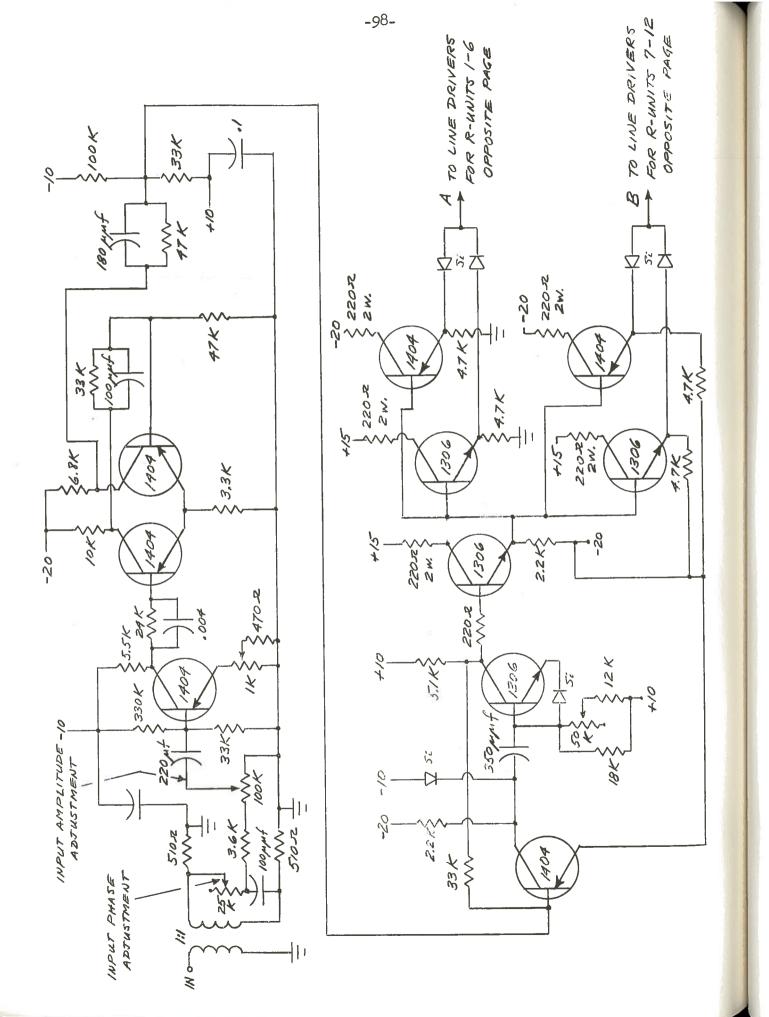

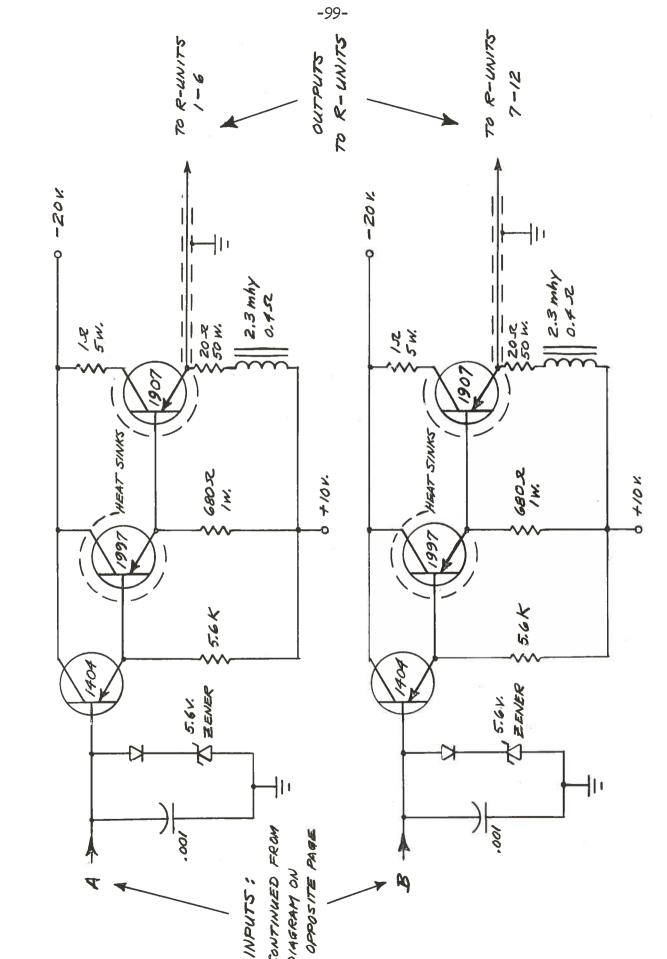

| 3.4.2 | Circuit Diagram for Phase Reference Source    | 98-99   |

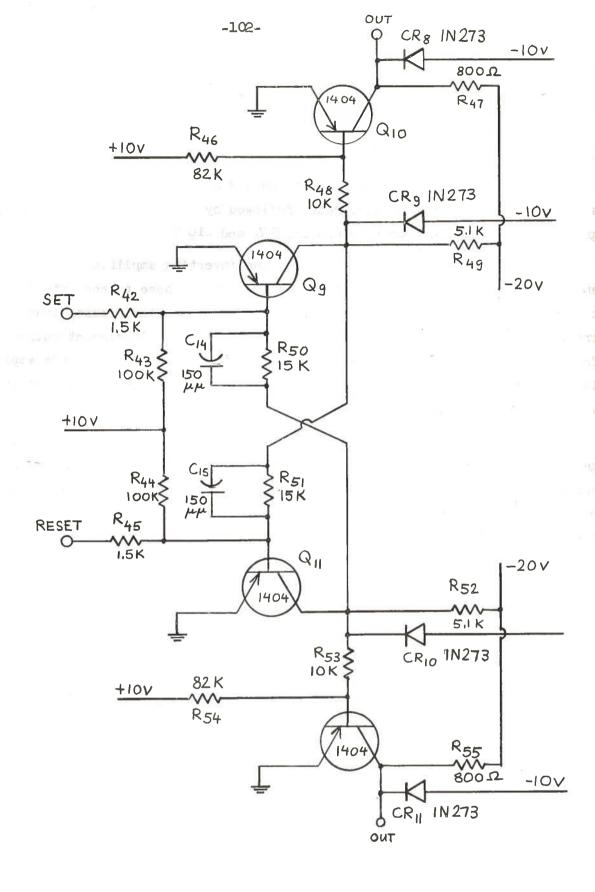

| 3.5.1 | R-Unit Flip-Flop                              | 102     |

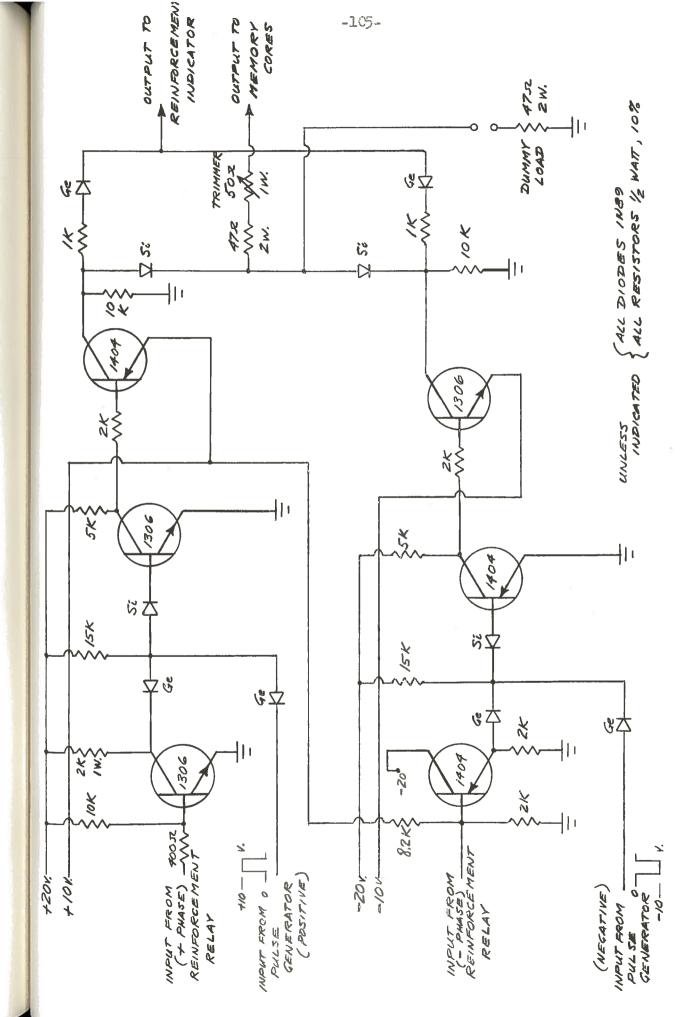

| 3.6.1 | Truth Table for Reinforcement Gates           | 104     |

| 3.6.2 | Pulse Reinforcement Gates                     | 105     |

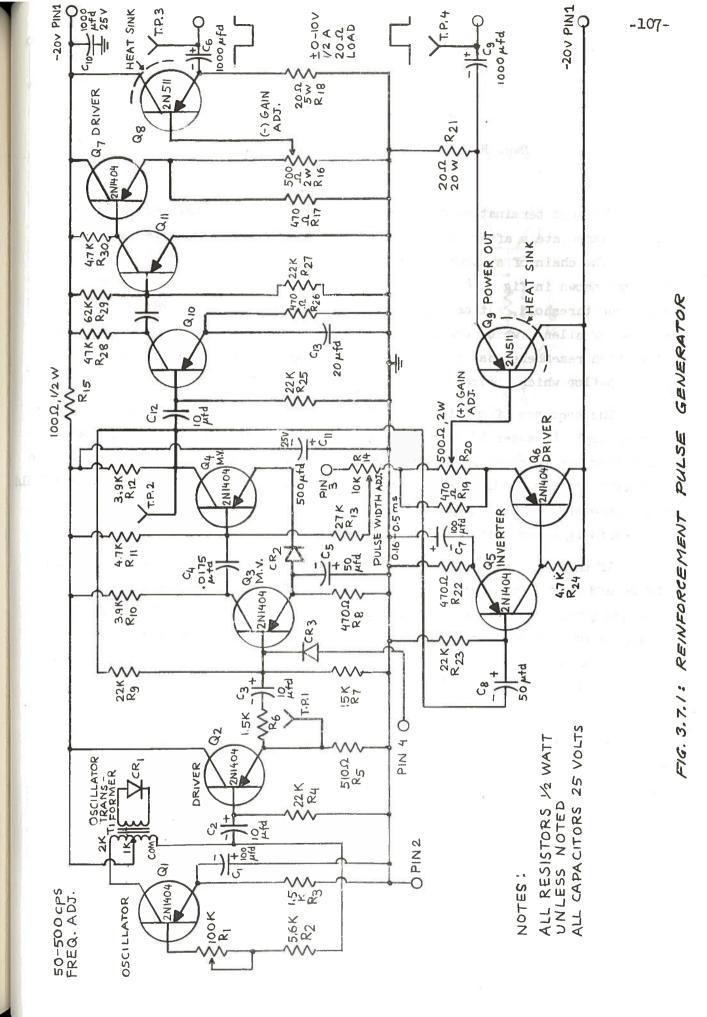

| 3.7.1 | Reinforcement Pulse Generator           | 107       |

|-------|-----------------------------------------|-----------|

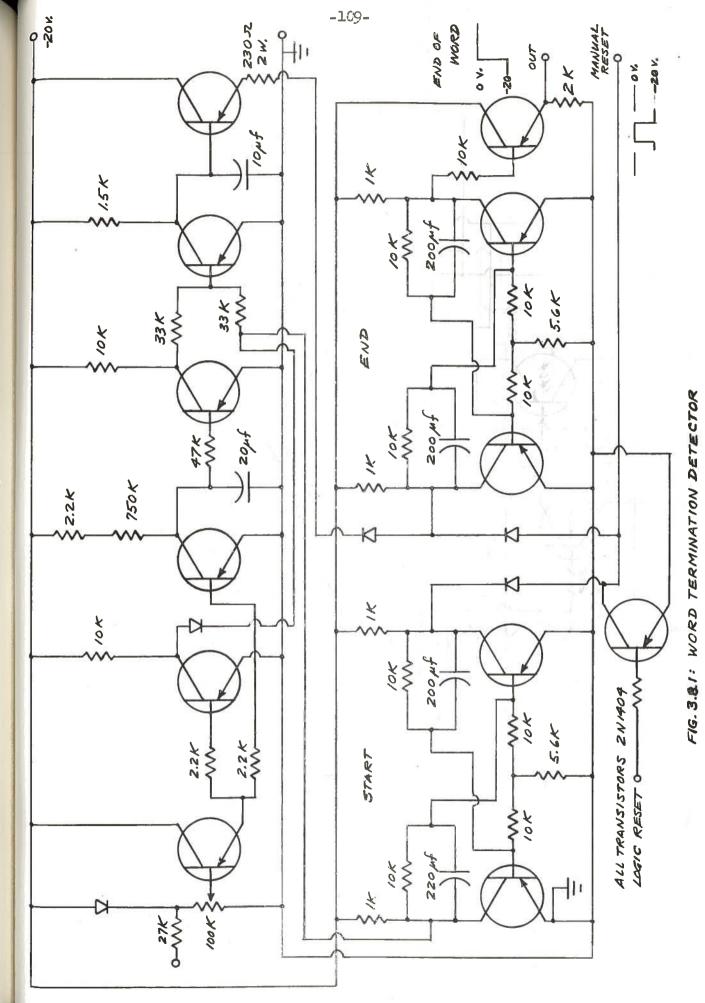

| 3.8.1 | Word Termination Detector               | 109       |

| 3.9.1 | Reinforcement Timing Control            | 110 - 111 |

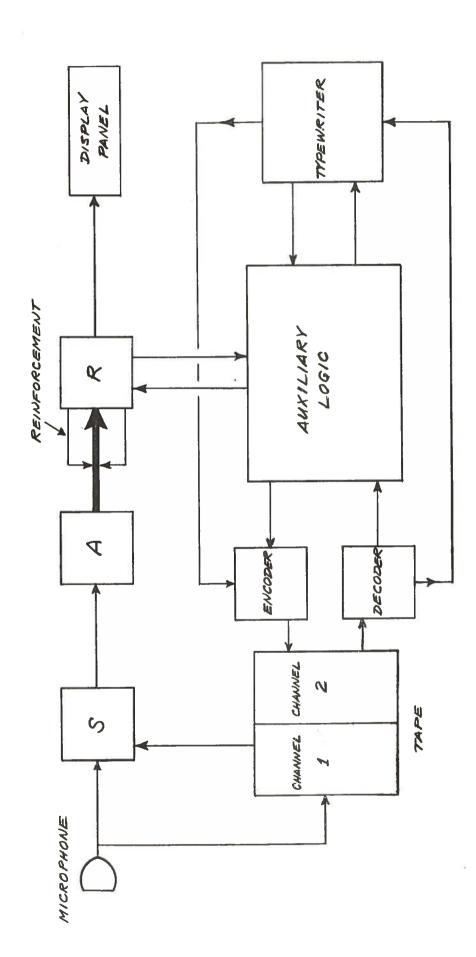

| 4.0.1 | Flow of Information in Tobermory System | 114       |

| 4.0.2 | Message Format on Tape                  | 115       |

| 4.0.3 | Printout Format                         | 116       |

### SUMMARY

Dwg. No. 1.2 Detailed System Design\*

Dwg. No. 1.1 Tobermory Floor Plan

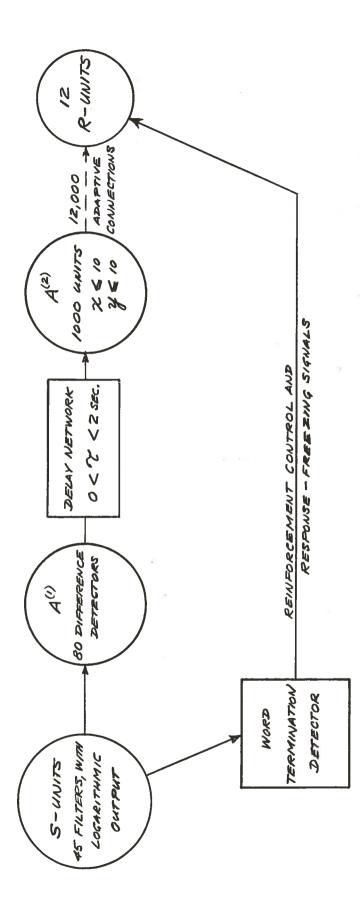

Tobermory, named after Saki's eavesdropping talking cat, is a general purpose pattern recognition machine roughly modelled on biological prototypes.† Phase I, described in this report, consists of a four-layer audioperceptron organized as shown in figure 0.0.1.

The sensory analyzer breaks up the signal into a 1600 bit time-frequency-amplitude pattern. The outputs of the sensory units are connected in many-to-many fashion to 1000 association units, which, in turn, are linked by 12,000 variable weights to 12 decision elements (response units). A given signal may thus be represented by one of 2<sup>12</sup> code words. This scheme is implemented as follows.

A microphone and a tapehead serve as alternative inputs to 45 resonant band pass filters. The bandwidth of the filters is manually variable in five steps, corresponding to Q's in the range of one to twelve, while the center frequencies may be changed in a two to one range. The center frequencies are distributed uniformly on a pitch (mel) scale. The logarithms of the outputs of the filters are pairwise compared in variable-threshold difference amplifiers. This operation serves to localize peaks, valleys, and sharp transitions in the instantaneous frequency profile. Provision is also made to monitor the overall amplitude level.

The outputs of the difference amplifiers constitute the input to eighty delay lines consisting of twenty monostable multivibrators each. The time delay associated with each multivibrator may be set independently in the range of 10 to 100 milliseconds, yielding asynchronous sampling of words up to two seconds long. The 1600 bit pattern represented by the multivibrators is

<sup>\*</sup> Drawings listed after section headings refer to CSRP file numbers.

References are listed at the end of the report.

TOBERMORY, F/G. 0.0.1:

available on a plugboard, which permits selection of arbitrary subsets as 'receptive fields' for each A-unit.

The A-units are simply difference amplifiers with a threshold setting. When the threshold is exceeded, a carrier signal is gated to each of the twelve analog memory elements associated with an A-unit, and a signal proportional to the setting of the tapewound cores is contributed to the appropriate R-unit, where all such signals are summed. The R-units are also threshold elements, with built-in hysteresis to increase stability.

In automatic operation, digital signals from one channel of the tape (representing the desired output) regulate reinforcement (incrementing or decrementing the flux levels in the cores). During training, the reinforcement history of each R-unit is printed out on an electric typewriter, which also serves to code the training tapes. A number of other convenient features facilitate experimentation on word and music recognition, continuous speech processing, language, regional accent, and individual speaker identification, phoneme structure analysis, and related problems.

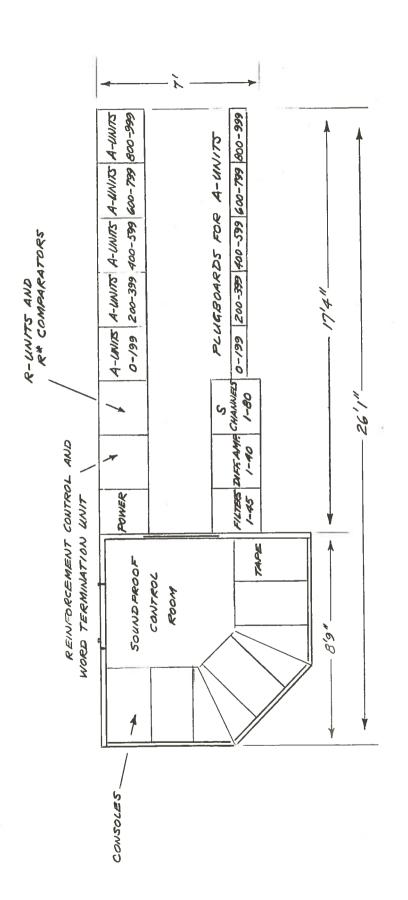

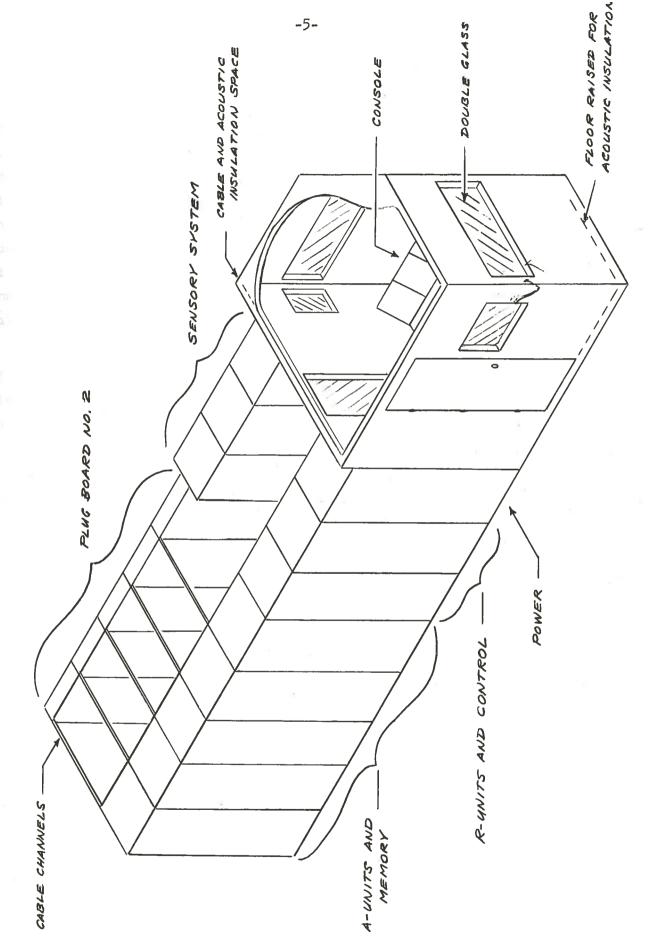

Figure 0.0.2 depicts the physical location of the various units described above, while figure 0.0.3 is an isometric sketch of the structure. Following presentation, the introductory sections cover the material in each chapter in block diagram form. The remaining sections contain detailed descriptions of the mode of operation and calibration of the circuits necessary to implement the block diagrams. The author hopes to relieve the repetitious, pedestrian style of these descriptions by the use of numerous apposite illustrations.

-4-

(SCALE 1:48) FLOOR PLAN TOBERMORY PHASE I F1G. 0.0.2:

FIG. 0.0.3: ISOMETRIC VIEW OF TOBERMORY, PHASE I

### CHAPTER I - THE SENSORY ANALYZER

### 1.0 - Introduction

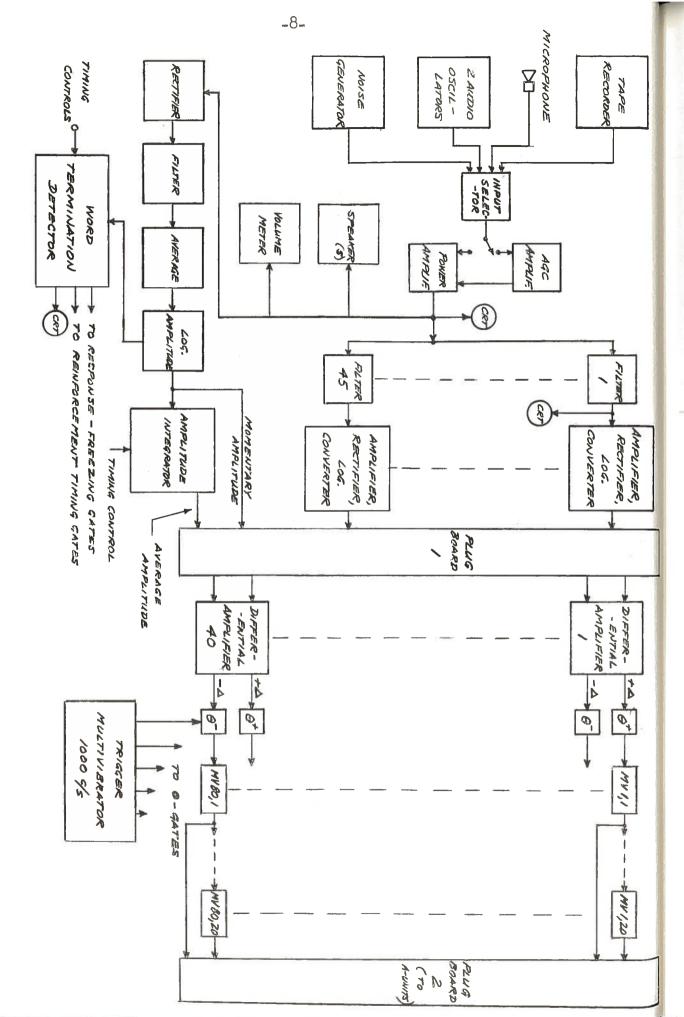

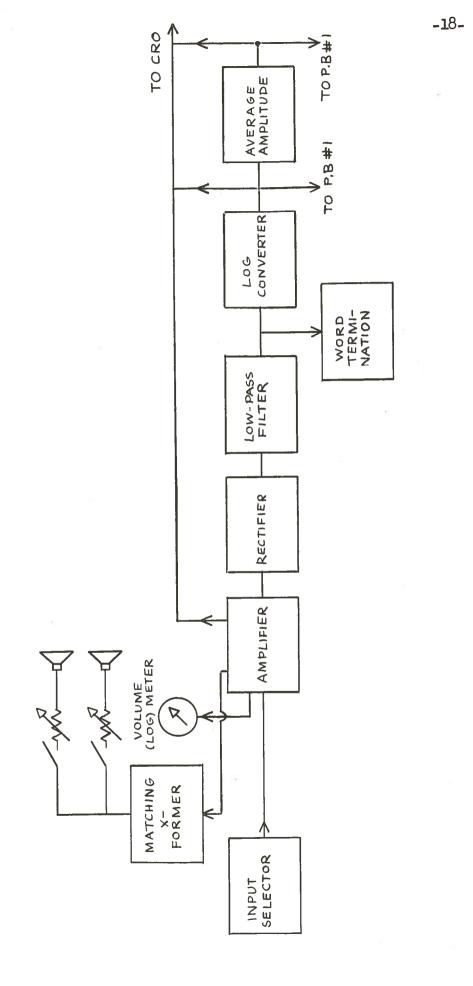

A detailed block diagram of the sensory analyzer, consisting of the audio input system, the  $A^{(1)}$  units, and the delay connections to the  $A^{(2)}$  units, is shown in figure 1.0.1.

The sensory input, dialed on the input selector in the control booth, can be any mixture of signals from a tape recorder, a microphone, a pair of audio oscillators, and a noise generator. An AGC amplifier with 25db. compression can be switched into the system at the operator's discretion. From here the signals are amplified for input to the filter network. The signal coming from the main amplifier is available for display on an oscilloscope in the control room, as are the outputs of the filters. The audio signal also goes to the monitoring speakers, a volume meter, and an amplitude measurement circuit which emits a voltage proportional to the average amplitude of the signal. This measurement is used to trigger the word termination (or pause) detector which is activitated by a period of silence following an audio input signal. It is also averaged over a longer time period, to provide information to the perceptron on the amplitude profile of the input pattern, which would otherwise be lost in the frequency analyzing network. Both the "momentary amplitude" and the "average amplitude" are available, along with the logarithms of the 45 filter outputs, at Plug Board no. 1.

The 45 audio filters can be set to cover one of three ranges: 30 to 4700 cps, 47 to 7000 cps, or 60 to 9400 cps. The bandwidths are variable from 8.4% to 100% of the center frequencies.

Each of the 40 differential amplifiers (representing the A<sup>(1)</sup> units of figure 0.0.1) can be connected to any pair of signals from filters or amplitude measuring devices by means of plug board no. 1. Since all of these signals are represented in logarithmic form, the signal from the differential amplifier represents the ratio of two amplitudes, rather than the absolute difference. This eliminates the need for a very high compression AGC amplifier, and

effectively normalizes the speech input for variability due to changes in volume, distance from the microphone, etc. Each differential amplifier has two output channels, one of which carries a signal if the difference is positive, and the other, if the difference is negative. Each difference signal is fed to a threshold gate with adjustable threshold. This system, then, extracts from the profile of the instantaneous frequency spectrum the ratios of the amplitudes at selected pairs of points throughout the spectrum. It is this set of ratios, now represented in digital form by the outputs of the 80 threshold gates, which characterizes the audio pattern for the subsequent parts of the system.

In order to represent the time dimension of the input pattern, the sets of eighty signals representing the momentary frequency spectrum are fed into eighty channels of twenty delay multivibrators each. Whenever a threshold gate is activated (indicating that some ratio of frequency amplitudes has exceeded its threshold) it permits a pulse from a trigger generator to touch off the first delay unit in the corresponding chain. This signal travels down the delay chain; the state of each multivibrator represents the output of the threshold gate at some previous instant of time. The 1600 individual multivibrator outputs are available at plugboard number 2, so that they may be connected to any combination of the 1000 A<sup>(2)</sup> units.

1.1 The Input Selector

Dwg. No. 3.2 The Input Selector

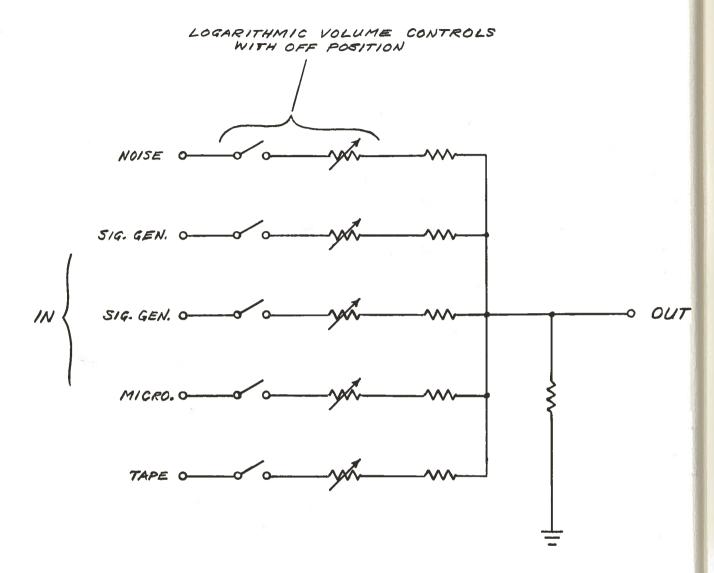

The input selector (Figure 1.1.1) is a resistive network designed to equalize the signal levels from the various input devices (microphone, tape recorder, two audio signal generators, and a noise generator) and render them accessible to the audio amplifier. The logarithmic potentiometers are chosen in such a way that at their maximum setting the output of the input selector is about 1 mv. p-t-p. The pots also have an "off" position. These potentiometers, mounted on the audio control panels, are normally used to adjust the amplitude according to the level shown on the amplitude level meter. The tape recorder, main audio amplifier, and AGC controls should be used for calibration purposes only.

Any mixture of signals, as well as any "pure" signal, may be obtained from the input selector. The noise generator is to be used mainly for simulating the effect of various levels of noise added to "clean" recordings. The audio oscillators are handy for adjusting threshold levels in the difference amplifiers; for this purpose, the control room oscilloscope may be used to monitor the two filter or amplitude channels, while the pilot lamp at the end of the sensory delay line to which the differential amplifier is connected indicates when the threshold has been exceeded.

FIG. 1.1.1: INPUT SELECTOR

### 1.2 Main Audio Amplifier

### Elco Manual

The main audio amplifier is an Electronic Instrument Co. Inc. (EICO) model HF-30 30 watt high fidelity integrated unit. Trouble shooting instructions are given in EICO Manual No. HF: 32-1.

Since all the inputs originate from the input selector, the microphone input and preamplifier are used under all conditions. The bass and treble compensation are set to the neutral (center) position, and the loudness control is turned fully clockwise to avoid low and high frequency emphasis. The rumble and scratch filters are left in the "off" position. The level control is adjusted to provide 100 mv. p-t-p signal at the input to the audio filters with maximum input from any of the signal generating devices connected to the input selector. With proper adjustment this should correspond to 5 on the level-setting dial.

A step-down audio transformer and a variable ratio voltage divider reduces the output of the amplifier (40 tap) to a level suitable for feeding into the filters. The aggregate input impedance of the filter bank is at least 5 ohms, so any arrangement which reduces the impedance level of the signal to below 1 ohm is satisfactory.

Note that it is imperative to use high quality shielded wire for all connections to and from the amplifier.

### 1.3 Automatic Gain Control Amplifier

### Dwg. No. 3.1 Automatic Gain Control Amplifier

The purpose of the automatic gain control amplifier (AGC) is to reduce the dynamic range requirements of subsequent stages. Without exceedingly cumbersome precautions, it is unreasonable to expect transistor circuits to handle analog quantities susceptible to a greater than 40 decibels (a factor of 100) variation. The AGC reduces the normal 65 db. range of the human voice (as picked up by a microphone) to an acceptable 40 dbs.

This amplifier is connected between the input selector (section 1.1) and the Eico power amplifier (section 1.2). A remote control relay permits bypassing the AGC altogether, at the operator's discretion. The relay also cuts off the high voltage and filament supply to the tubes.

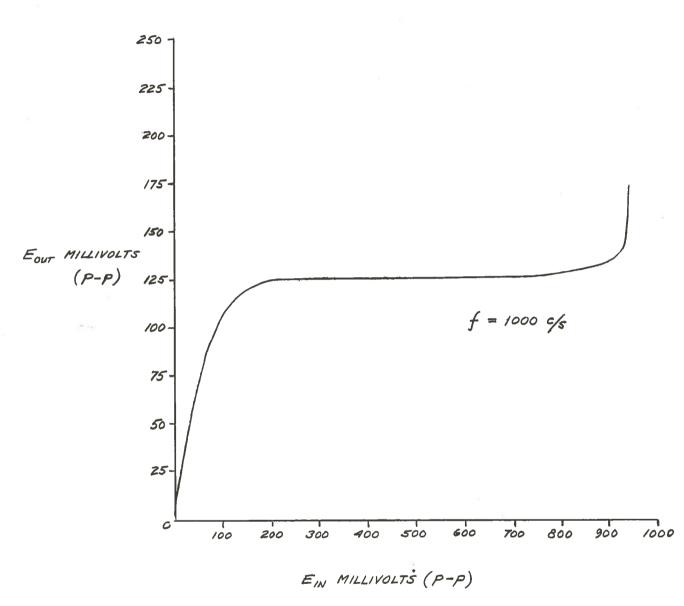

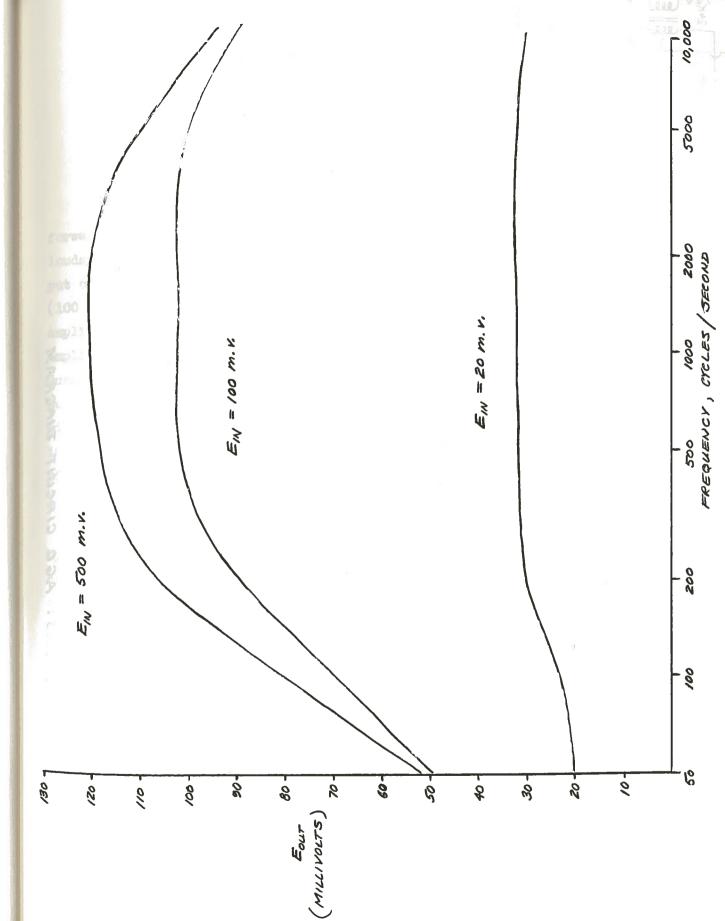

The control action of the AGC is shown on Fig. 1.3.1, and the frequency response on Fig. 1.3.2. The output is free of noticeable distortion except below 100 cps. The minimum attack time (measured to 90 per cent of the final response) is about 15 msecs, while the release time is of the order of 1 second. Both of these time constants are adjustable by means of front panel potentiometers.

The AGC (circuit schematic on Fig. 1.3.3) has a low noise, high impedance input, suitable for direct connection to any (except carbon button) common microphone. Provision is made on the front panel to adjust the gain of the input section to different microphones. The single ended output is designed to feed into a load impedance of at least 50,000 chms.

The heart of the control action lies in the circuitry associated with the double triode V4. This will be recognized to constitute an unbalanced bridge. Since the plate resistance of the V4 is strongly dependent upon its grid-to-cathode voltage, the signal voltage developed between the output nodes of the bridge is also a function of this grid-to-cathode voltage. This voltage, in turn, is proportional to the amplitude of the input signal, due to the action of A.C. amplifier V6, bridge rectifiers V7 and V8, and D.C. amplifier V9. Note that the amount of control is directly dependent upon the input signal. There is no feedback loop of any kind in the amplifier, hence phase shift and

oscillation problems do not arise.

For initial adjustment (after tube or component changes), it is necessary to warm up the amplifier for at least an hour. Connect a 1000 cps signal generator to the input, and set the level to about 250 mv. Adjust the two level controls, on the panel and on the chassis, to their half way points, and monitor the output with an oscilloscope. Then alternately advance the two settings until distortion in the output is noticed. At this point, the signal voltage across the load resistors of V3 will be about 80 volts peak to peak. Now connect the oscilloscope to the plates of V8 (white wire marked with blue), and adjust the chassis balance control until alternate peaks of the waveform are of equal height. This is necessary to limit distortion at low frequencies, since the output of the bridge rectifier is only capacitively filtered in order to avoid time lags.

Now replace the signal generator with the microphone to be used, and measure the maximum input generated by talking loudly into the microphone at close range. Set the signal generator at the measured level, and substitute it for the microphone. Then adjust the panel level control for maximum output without distortion. The AGC is now ready for action.

Some low frequency distortion will occur before the amplifier is fully warmed up, but this will usually affect only a deep male voice. Distortion may also occur if the supply voltage is not kept at exactly 210 volts.

-15-

FIG. 1.3.1: AMPLITUDE RESPONSE OF AGC AMPLIFIER

SUPPLY

. . .

日区

AMPLIFI

SECTION

CONTROL

1004

12AX7

+210V DC

9889

FSOK LOAD

120 K

20

5×1

R8 X

9889

74.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7.24 × 7

FILAMENT SUPPLY

FOR REMOTE

SWITCH

RELAY)

POLE

(3-

œ

$\overline{\alpha}$

6386

65N7

£ 30 1+1−

0

### 1.4 Volume Monitors

Dwg. No. 3.3 Loudspeaker Controls

4.2.4 Volume Detector Amplifier

4.2.5 Average Amplitude Detector

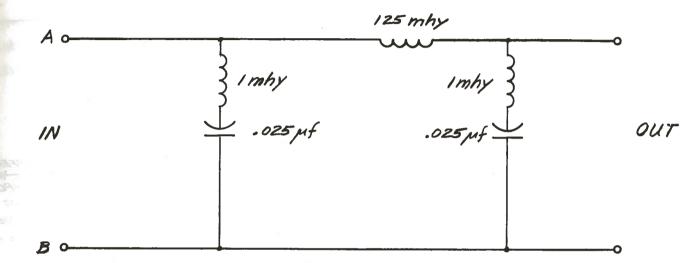

The volume monitoring system, shown on figure 1.4.1, is quite straightforward. The signal from the input selector (section 1.1) is fed to two loudspeakers through a matching transformer and volume control pads. The output of the input selector is also displayed on the logarithmic volume meter (100 mv full scale deflection) and serves as input to the volume detector amplifier. This amplifier (figure 1.4.2) is similar to the forty-five audio amplifiers described in section 1.6. The smoothing circuit is borrowed from Gunnar Fant's "Acoustic Analysis and Synthesis of Speech with Applications to Swedish"; it is an optimum phase designed LRC whole section low pass filter with a cut off frequency of 300 radians per second (about 50cps). The nominal impedance of 8000 ohms satisfies both the amplifier and the parallel combination of the inputs of the word termination detector (section 3.8) and the standard log converter without any impedance matching other than a 60 KO bleeder.

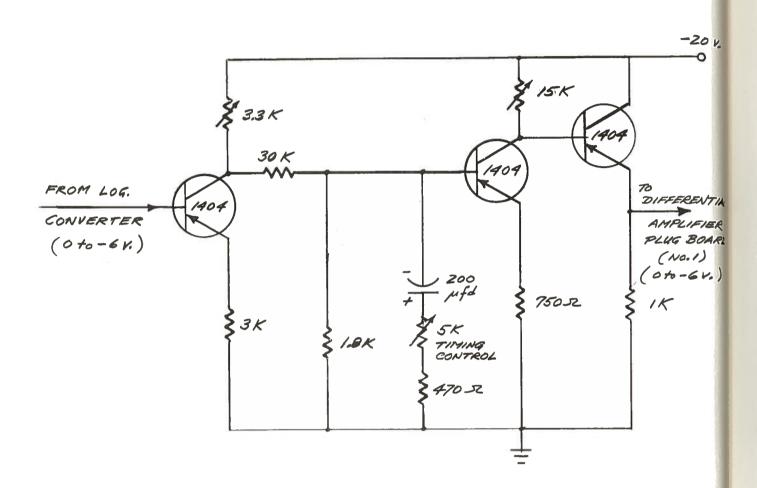

The average amplitude indicator (fig. 1.4.3) is an R-C integrator isolated by two inverting amplifiers. The net gain of this circuit is unity. The time constant of the integrator may be varied from 0.1 second to 1.0 second by means of potentiometer R1.

Provisions are made to monitor on the screen of the control room oscilloscope the total speech waveform injected into the perceptron, the momentary amplitude, and the average amplitude.

Note that either the momentary amplitude or the average amplitude signal may be used with any frequency channel for comparison in a difference amplifier. The signals, as found on plug board number one, are compatible.

DIAGRAM

BLOCK

ATTACHED TO AMPLIFIER IDENTICAL WITH

FIG. 1.6.1, AT POINTS "A" AND "B", SUBSTITUTING

FOR CIRCUIT TO RIGHT OF A-B IN FIG. 1.6.1

FIG. 1.4.2: FILTER FOR AUDIO MONITOR AMPLIFIER

FIG. 1.4.3: AVERAGE AMPLITUDE INDICATOR

### 1.5 Audio Filters

Dwg. No. 4.2.1 Filter Amplifier and Log Converter 2.6 Rack No. 1, Front View

The 45 audio filters (fig. 1.5.1) are series resonant L-C circuits using high-Q inductors. The center frequencies are uniformly distributed on the pitch (mel) scale, which roughly approximates human audio response. The equivalence between pitch and frequency may be expressed by

$$P = \frac{1000}{\log 2} \log (1 + \frac{f}{1000})$$

where P is in mels and f is in cycles per second

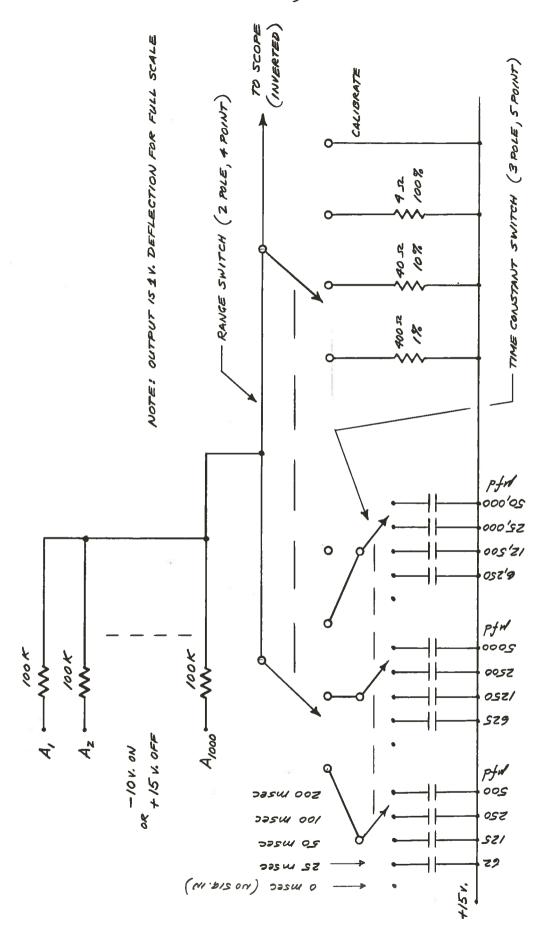

This equation is plotted in fig. 1.5.2. In addition to its center frequency  $f_2$ , each filter may be tuned to  $f_1$  and to  $f_3$  by switching capacitors.  $f_1$  has been chosen equal to  $\frac{2}{3} f_2$ , and  $f_3$  equal to  $\frac{2}{2} f_2$ . The ranges attainable by the different settings are plotted on both pitch and frequency scales in fig. 1.5.3.

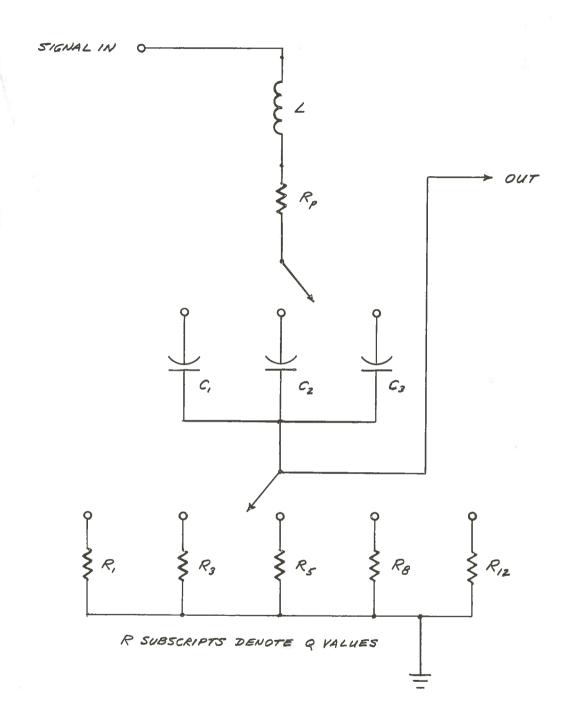

The output is the voltage developed across a series resistor. The five values of resistance which may be switched in here yield bandwidths corresponding to factors of merit (Q) of 1, 3, 5, 8, and 12. The Q and the bandwidth are related by  $EW = \frac{f}{Q}$ . The resistance values here have been chosen to be large compared to the internal equivalent resistance of the inductors (that of the capacitors is negligible) so that at resonance most of the input voltage is developed across the output resistor.

Since only the relative amplitudes of the filter outputs are taken into account by the difference amplifiers, the change of about 20% in amplitude as the Q is changed from 1 to 12 is immaterial as long as the two filters connected to a single difference amplifier are both set to the same Q. In a further effort to minimize output amplitude variation with frequency, each inductor was padded with a series resistance to present an unloaded Q of 40 at the center frequency.

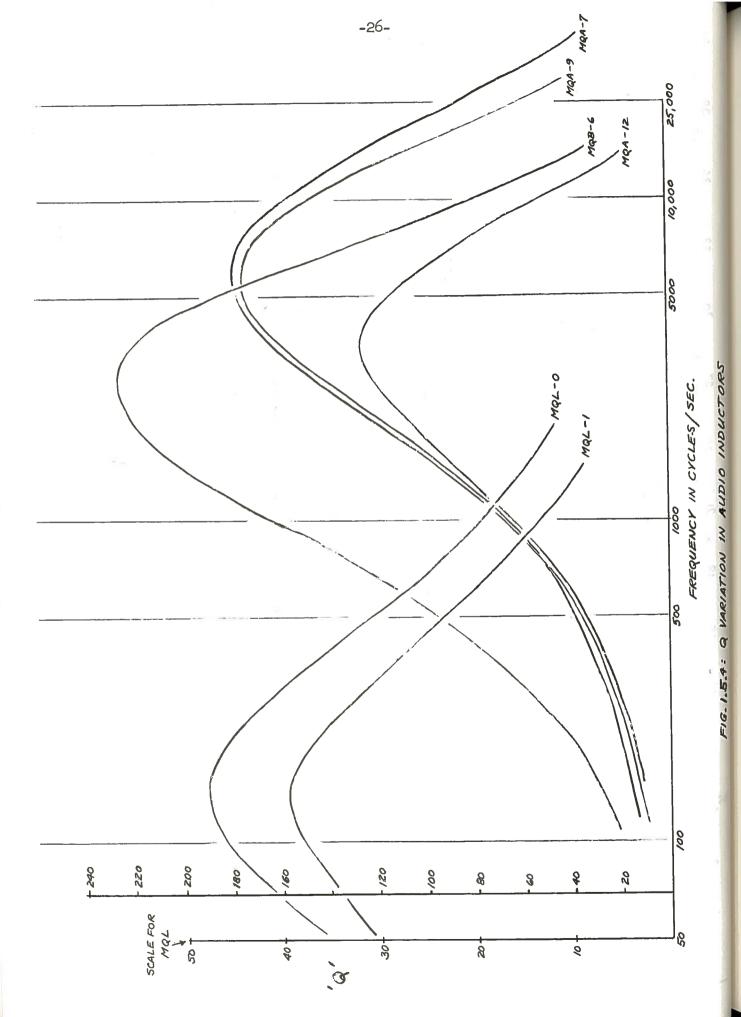

The 1962-63 United Transformer Corporation Catalogue on Electric Wave

Filters and High Q Coils covers the overall characteristics of inductors used in the audio filters, while fig. 1.5.4 shows the representative Q vs. frequency plots of the different units. It is to be noted that for best performance, the inductors should be used at low (mv) voltage levels.

The capacitors are +0%, -5% tolerance components padded with small mica capacitors to resonate with the coils at the design frequencies. To keep the bandwidth and the resonant gain as constant as possible, precision resistors were used throughout.

The design values of the various components appear in Figure 1.5.5.  $R_L$  refers to the internal equivalent resistance of the inductor measured at the center frequency,  $R_p$  is the value of the padding resistor required to bring the Q down to 40, the  $r_i$ 's are the resistance values, which, in combination with  $R_L$  and  $R_p$  would yield the appropriate filter bandwidths, and the  $R_i$ 's are the actual resistors on the filter panels.  $R_i$  in parallel with the input resistance of the next stage is equal to  $r_i$ .

Figure 1.5.6 shows the measured resonant frequencies and bandwidth of the 45 filters with all possible settings.\*

FIG. 1.5.1: AUDIO FILTER CIRCUIT DIAGRAM

other approaches were explored. Odarchenko (see Filter and Multivibrator by A. Odarchenko) worked on a continuously variable center frequency filter based on the well known parallel. T null network. The chief difficulty here was interaction between frequency and bandwidth adjustments, and insufficient frequency variability. Liskov tried shifting the poles of a two-stage R-C filter with an active feedback network, but could not obtain a sufficiently narrow bandwidth without oscillations. Commercial variable parameter bandpass filters begin at about \$250 a piece. A firm of consulting engineers submitted a bid for the whole filter network at \$8000. In view of these impasses, the several requirements for the filters were somewhat relaxed, resulting in the adoption of the resonant L-C circuit. Components for the latter averaged about \$20 a filter.

Figure 1.5.5 Component Walues for Audio Filters

| F  | fc           | BW <sub>1</sub> | BW <sub>2</sub> | BW <sub>3</sub> | BW <sub>4</sub> | BW <sub>5</sub> | $\mathtt{Q}_{\mathtt{l}}$ | g <sub>2</sub> | Q3  | $Q_{14}$ | Q <sub>5</sub> |

|----|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------------------------|----------------|-----|----------|----------------|

| 1  | 31.6         | 51              | 17.1            | 10.4            | 7               | 5.1             | .62                       | 1.8            | 3   | 4.5      | 6.2            |

|    | 47.5         | 53.4            | 17.6            | 10.8            | 7               | 5.5             | .89                       | 2.7            | 4.4 | 6.8      | 8.7            |

|    | 63.2         | 49              | 17.2            | 11              | 7•2             | 5.5             | 1.3                       | 3.7            | 5.7 | 8.8      | 11.5           |

| 2  | 66           | 109.3           | 36.2            | 21.8            | 13.7            | 9.5             | .6                        | 1.8            | 3.  | 4.8      | 7.             |

|    | 96           | 90.7            | 33.             | 23.8            | 13.2            | 10              | 1.1                       | 2.9            | 4.  | 7.3      | 9.1            |

|    | 128          | 100.4           | 34.8            | 22              | 14              | 10.5            | 1.3                       | 3.8            | 5.8 | 9.2      | 12.2           |

| 3  | 100          | 129.8           | 46.6            | 28.6            | 17.5            | 12.4            | .78                       | 2.1            | 3.5 | 5.7      | 8.1            |

|    | 149          | 120             | 48              | 31              | 20.5            | 14.5            | 1.2                       | 3.1            | 4.8 | 7.3      | 10.3           |

|    | 200          | 170             | 60              | 35              | 33              | 18              | 1.2                       | 3.3            | 5.7 | 6.1      | 11.1           |

| 4. | 135          | 177.5           | 65.5            | 42.7            | 25              | 16              | .76                       | 2.1            | 3.2 | 5.4      | 8.5            |

|    | 202          | 209.5           | 80              | 49              | 30              | 21.5            | .97                       | 2.5            | 4.1 | 6.7      | 9.4            |

|    | 270          | 142             | 73              | 45              | 30              | 20              | 1.9                       | 3.7            | 6   | 9        | 13.5           |

| 5  | 173          | 277             | 77              | 55              | 38              | 33              | .63                       | 2.3            | 3.2 | 4.6      | 5.3            |

|    | 259          | 286             | 92              | 61              | 46              | 36              | .91                       | 2.8            | 4.3 | 5.6      | 7.2            |

|    | 346          | 265             | 100             | 65              | 47              | 42              | 1.2                       | 3.5            | 5.3 | 7.4      | 8.2            |

| 6  | 212          | 330             | 105             | 67              | 46              | 34              | .64                       | 2              | 3.2 | 4.6      | 6.2            |

|    | 318          | 310             | 118             | 61              | 43              | 36              | 1.                        | 2.7            | 5.2 | 7.4      | 8.9            |

|    | 424          | 294             | 112             | 78              | 55              | 48              | 1.4                       | 3.8            | 5.5 | 7.7      | 8.8            |

| 7  | 254          | 388             | 128             | 81              | 51              | 37              | .66                       | 2.             | 3.1 | 5.       | 6.9            |

|    | 381          | 362             | 140             | 69              | 50              | 41              | 1.                        | 2.7            | 5.5 | 7.6      | 9.3            |

|    | 508          | 356             | 139             | 94              | 64              | 54              | 1.4                       | 3.6            | 5.4 | 8.       | 9.4            |

| 8  | 297          | 463             | 121             | 82              | 56              | 44              | .64                       | 2.5            | 3.6 | 5.3      | 6.8            |

|    | 450          | 483             | 152             | 95              | 63              | 42              | .93                       | 3.             | 4.7 | 7.2      | 10.7           |

|    | 594          | 4 <b>0</b> 2    | 137             | 79              | 62              | 47              | 1.5                       | 4.3            | 7.5 | 9.6      | 12.6           |

| 9  | 343          | 7 <b>0</b> 3    | 230             | 135             | 104             | 83              | .49                       | 1.5            | 2.5 | 3·3      | 4.1            |

|    | 514          | 619             | 185             | 126             | 90              | 70              | .83                       | 2.8            | 4.1 | 5·8      | 7.4            |

|    | 686          | 472             | 146             | 107             | 71              | 52              | 1.4                       | 4.7            | 6.4 | 9·7      | 13.2           |

| 10 | 390          | 617             | 189             | 112             | 66              | 52              | .63                       | 2.1            | 3.5 | 5.9      | 7.5            |

|    | 585          | 702             | 2 <b>0</b> 5    | 131             | 89              | 60              | .83                       | 2.9            | 4.5 | 6.6      | 9.8            |

|    | 780          | 464             | 197             | 126             | 84              | 60              | 1.7                       | 4.             | 6.2 | 9.3      | 13.            |

| п  | 439          | 665             | 225             | 145             | 85              | 69              | .66                       | 2.             | 3.  | 5.2      | 6.4            |

|    | 664          | 593             | 217             | 136             | 89              | 65              | 1.1                       | 3.1            | 4.9 | 7.5      | 10.2           |

|    | 8 <b>7</b> 5 | 600             | 203             | 142             | 96              | 90              | 1.5                       | 4.3            | 6.2 | 9.1      | 9.7            |

| F fc                             | BW <sub>1</sub> | BW2                           | 2 F | BW <sub>3</sub>   | BW <sup>1</sup>   | BW <sub>5</sub>   | $\mathbf{Q}_{\mathbf{l}}$ | Q2                | Q <sub>3</sub>    | Q <sub>14</sub>    | <b>Q</b> <sub>5</sub> | F  | fc                   | BWl                  | BW <sub>2</sub>           | BW <sub>3</sub>           | BW <sub>4</sub>   | <b>BW</b> <sub>5</sub> | Q <sub>1</sub>    | e <sup>2</sup>    | Q <sub>3</sub>    | Q <sub>14</sub>    | Q <sub>5</sub>      |

|----------------------------------|-----------------|-------------------------------|-----|-------------------|-------------------|-------------------|---------------------------|-------------------|-------------------|--------------------|-----------------------|----|----------------------|----------------------|---------------------------|---------------------------|-------------------|------------------------|-------------------|-------------------|-------------------|--------------------|---------------------|

| 492<br>12 747<br>980             |                 | 246<br>25]<br>213             | L J | 163<br>158<br>154 | 104<br>104<br>103 | 74<br>70<br>75    | .67<br>1.1<br>1.4         | 2<br>3<br>4.6     | 3<br>4.7<br>6.4   | 4.7<br>7.2<br>9.5  | 5.2<br>10.7<br>13     | 24 | 1355<br>2032<br>2710 | 2060<br>2090<br>2090 | 660<br>550<br>650         | 435<br>440<br>440         | 290<br>280<br>300 | 210<br>215<br>230      | .66<br>.97<br>1.3 | 2.1<br>3.7<br>4.2 | 3.1<br>4.6<br>6.2 | 4.7<br>7.3<br>9.   | 6.5<br>9.5<br>11.8  |

| 547<br>13 820<br>110             |                 | 285<br>270<br>251             | o : | 174<br>167<br>164 | 109<br>102<br>112 | 82<br>79<br>86    | .66<br>.98<br>1.4         | 1.9<br>3.<br>4.3  | 3.1<br>4.9<br>6.7 | 5.<br>8.<br>9.8    | 6.7<br>10.4<br>12.8   | 25 | 1450<br>2200<br>2900 | 1920<br>2420<br>2280 | 725<br>770<br>740         | 460<br>500<br>420         | 300<br>310<br>290 | 220<br>220<br>200      | .76<br>.91<br>1.3 | 2.<br>2.9<br>3.9  | 3.2<br>4.4<br>6.9 | 4.8<br>7.4<br>10.  | 6.6<br>10.<br>14.5  |

| 603<br>14 908<br>121             | 977             | 318<br>318<br>290             | 3 : | 183<br>192<br>175 | 114<br>123<br>120 | 82<br>80<br>90    | .67<br>.93<br>1.4         | 2.<br>2.9<br>4.2  | 3·3<br>4·7<br>7·  | 5.3<br>7.4<br>10.1 | 7.4<br>11.4<br>13.5   | 26 | 1570<br>2324<br>3098 | 2070<br>2510<br>2370 | 780<br>750<br>650         | 480<br>490<br>460         | 305<br>340<br>300 | 200<br>240<br>230      | .76<br>.93<br>1.3 | 2.<br>3.1<br>4.8  | 3·3<br>4.8<br>7·  | 5.2<br>6.9<br>10.3 | 7.8<br>9.7<br>13.4  |

| 667<br>15 100<br>133             | 8 1006          | 303<br>35 <sup>1</sup><br>320 | 4 : | 196<br>196<br>200 | 128<br>128<br>130 | 88<br>87<br>100   | .68<br>1.<br>1.4          | 2.2<br>3.1<br>4.2 | 3.4<br>5.5<br>6.7 | 5.2<br>8.4<br>10.3 | 7.6<br>12.4<br>13.3   | 27 | 1660<br>2500<br>3296 | 2040<br>2710<br>2560 | 780<br>740<br>810         | 500<br>470<br>490         | 330<br>300<br>320 | 240<br>230<br>240      | .81<br>.92<br>1.3 | 2.1<br>3.4<br>4.1 | 3.3<br>5.3<br>6.7 | 5.<br>8.3<br>10.3  | 6.9<br>10.2<br>13.7 |

| 731<br>16 115<br>146             | 0 1285          | 38                            | 5   | 210<br>250<br>205 | 142<br>157<br>150 | 101<br>117<br>100 | .71<br>.9<br>1.3          | 2.2<br>3.<br>4.2  | 3.5<br>4.6<br>7.1 | 5.2<br>7.3<br>9.8  | 7.2<br>9.8<br>12.2    | 28 | 1763<br>2645<br>3526 | 2200<br>3160<br>3210 | 845<br>870<br>870         | 560<br>560<br>520         | 340<br>390<br>360 | 250<br>280<br>260      | .8<br>.84<br>1.1  | 2.1<br>3.<br>4.   | 3.1<br>4.7<br>6.8 | 5.2<br>6.8<br>9.8  | 7.1<br>9.4<br>13.5  |

| 796<br>17 119<br>159             | 4 139           | 0 41                          | 5   | 224<br>240<br>240 | 125<br>160<br>150 | 105<br>122<br>120 | .62<br>.86<br>1.4         | 2.2<br>2.9<br>5.4 | 3.6<br>5.<br>6.6  | 6.4<br>7.5<br>10.6 | 7.6<br>9.8<br>13.3    | 29 | 1879<br>2818<br>3758 | 2460<br>3350<br>2650 | 895<br>980<br>8 <b>70</b> | 535<br>590<br>580         | 360<br>390<br>360 | 260<br>250<br>260      | .76<br>.84<br>1.4 | 2.1<br>2.9<br>4.3 | 3.5<br>4.8<br>6.5 | 5.2<br>7.2<br>10.4 | 7.2<br>11.3<br>14.4 |

| 866<br>18 129<br>172             | 8 141           | 7 41                          | 5   | 296<br>257<br>260 | 183<br>155<br>170 | 148<br>120<br>120 | .67<br>.92<br>1.3         | 2.<br>3.1<br>5.4  | 2.9<br>5.1<br>6.6 | 4.7<br>8.4<br>10.1 | 5.9<br>10.8<br>14.4   | 30 | 1998<br>2999<br>3996 | 2610<br>3530<br>2790 | 1060<br>1080<br>850       | 600<br>590<br>580         | 380<br>400<br>380 | 280<br>270<br>290      | .77<br>.85<br>1.4 | 1.9<br>2.8<br>4.7 | 3.3<br>5.1<br>6.9 | 5.3<br>7.5<br>10.5 | 7.2<br>11.1<br>13.8 |

| 938<br>19 140<br>187             | 6 151           | 5 1414                        | 5   | 282<br>280<br>305 | 180<br>175<br>180 | 110<br>120<br>120 | .68<br>.93<br>1.4         | 2.<br>3.2<br>4.   | 3.3<br>5.<br>6.2  | 5.2<br>8.<br>10.4  | 8.5<br>11.7<br>15.6   | 31 | 2125<br>3187<br>4250 | 3040<br>3290<br>3340 | 1080<br>1070<br>1040      | 645<br>630<br>670         | 430<br>440<br>420 | 300<br>320<br>300      | •7<br>•97<br>1.3  | 2.<br>3.<br>4.1   | 3.3<br>5.1<br>6.3 | 5.<br>7.2<br>10.1  | 7.1<br>10.<br>14.1  |

| 101<br>20 152<br>20 <sup>1</sup> | 20 156          | 5 49                          | 0   | 292<br>315<br>310 | 182<br>205<br>210 | 137<br>140<br>160 | .61<br>•97<br>1.4         | 2.<br>3.1<br>4.2  | 3.5<br>4.8<br>6.6 | 5.6<br>7.4<br>9.7  |                       | 32 | 2257<br>3385<br>4515 | 3140<br>3360<br>3410 | 1160<br>1110<br>1170      | 690<br>690<br>670         | 450<br>450<br>440 | 300<br>310<br>330      | .72<br>1.<br>1.3  | 1.9<br>3.<br>3.8  |                   | 5.<br>7.5<br>10.2  | 7.5<br>10.9<br>13.7 |

| 109<br>21 169<br>21              | 38 168          | 0 56                          | 5   | 613<br>335<br>340 | 415<br>215<br>215 | 310<br>150<br>150 | •59<br>•98<br>13•4        | 2.9               | 1.8<br>4.9<br>6.4 | 2.6<br>7.6<br>10.2 |                       | 33 | 2396<br>3594<br>4792 | 3240<br>3690<br>3690 | 1170<br>1160<br>1130      | 740<br>700<br>700         | 470<br>470<br>450 | 330<br>340<br>340      | •74<br>•98<br>1•3 | 2.<br>3.1<br>4.2  | 3.2<br>5.1<br>6.9 | 5.1<br>7.7<br>10.6 | 7.3<br>10.6<br>14.1 |

| 22 170<br>23 23                  | 50 101          | 0 49                          | 90  | 320<br>305<br>300 | 210<br>215<br>220 | 150<br>160<br>170 | 1.1<br>1.7<br>2.1         | 2.5<br>3.6<br>5.6 | 3.6<br>5.8<br>7.8 | 5.6<br>8.2<br>10.7 |                       | 34 | 2540<br>3810<br>4960 | 4030<br>3710<br>3770 | 1350<br>1170<br>1100      | 760<br>740<br>730         | 490<br>490<br>480 | 330<br>360<br>340      | .63<br>1.<br>1.3  | 1.9<br>3.2<br>4.5 | 3.3<br>5.2<br>6.8 | 5.2<br>7.8<br>10.3 | 7.7<br>10.6<br>14.6 |

| 12<br>23 18<br>25                | 93 150          | 0 58                          | 30  | 370<br>285<br>340 | 240<br>230<br>240 | 180<br>190<br>180 | .71<br>1.3<br>1.5         | 2.<br>3.3<br>4.7  | 3.4<br>6.6<br>7.4 | 8.2                | 7.<br>10.<br>14.      | 35 | 2691<br>4037<br>5382 | ታታት0<br>ትታት0<br>ት220 | 1220<br>1290<br>1270      | 79 <b>0</b><br>790<br>790 | 510<br>520<br>530 | 340<br>360<br>340      |                   | 2.2<br>3.1<br>4.2 | 3.3<br>5.1<br>6.8 | 5.3<br>7.8<br>10.1 | 7.9<br>11.2<br>15.8 |

| F          | fc   | BW <sub>1</sub> | BW <sub>2</sub> | <b>BW</b> 3 | BW <sub>4</sub> | <b>BW</b> <sub>5</sub> | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> | Q <sub>14</sub> | Q <sub>5</sub> |

|------------|------|-----------------|-----------------|-------------|-----------------|------------------------|----------------|----------------|----------------|-----------------|----------------|

| 36         | 2857 | 4235            | 1430            | 850         | 560             | 380                    | .68            | 2.             | 3.4            | 5.1             | 7.5            |

|            | 4285 | 5020            | 1550            | 930         | 610             | 450                    | .85            | 2.8            | 4.6            | 7.              | 9.5            |

|            | 5730 | 3820            | 1340            | 820         | 520             | 380                    | 1.5            | 4.3            | 7.             | 11.             | 15.            |

| 37         | 3017 | 4560            | 1425            | 980         | 570             | 390                    | .66            | 2.1            | 3.1            | 5.3             | 7.7            |

|            | 4525 | 5370            | 1570            | 950         | 600             | 430                    | .84            | 2.9            | 4.8            | 7.5             | 10.5           |

|            | 6090 | 4370            | 1385            | 820         | 560             | 390                    | 1.4            | 4.4            | 7.4            | 10.8            | 15.5           |

| 38         | 3191 | 5160            | 1500            | 930         | 580             | 420                    | .7             | 2.1            | 3.4            | 5.5             | 7.6            |

|            | 4787 | 5470            | 1540            | 890         | 580             | 400                    | .88            | 3.1            | 5.4            | 8.3             | 12.            |

|            | 6382 | 4570            | 1490            | 870         | 590             | 430                    | 1.4            | 4.3            | 7.3            | 10.8            | 14.8           |

| 39         | 3374 | 4625            | 1570            | 1040        | 690             | 500                    | •73            | 2.1            | 3.2            | 4.9             | 6.8            |

|            | 5061 | 5920            | 1600            | 1000        | 700             | 490                    | •86            | 3.2            | 5.1            | 7.2             | 10.3           |

|            | 6748 | 4800            | 1620            | 1000        | 690             | 500                    | 1.4            | 4.2            | 6.7            | 9.8             | 13.5           |

| 40         | 3564 | 5130            | 1550            | 1060        | 700             | 505                    | .7             | 2.3            | 3.4            | 5.1             | 7.1            |

|            | 5346 | 6290            | 1760            | 1060        | 760             | 540                    | .85            | 3.             | 5.             | 7.              | 9.9            |

|            | 7128 | 5510            | 1800            | 1070        | 710             | 530                    | 1.3            | 4.             | 6.7            | 10.             | 13.4           |

| 41         | 3764 | 6040            | 1860            | 1150        | 800             | 540                    | .62            | 2.             | 3.3            | 4.7             | 7.             |

|            | 5646 | 4670            | 1840            | 1110        | 760             | 450                    | 1.2            | 3.1            | 5.1            | 7.4             | 12.5           |

|            | 7450 | 5200            | 1850            | 1190        | 750             | 580                    | 1.4            | 4.             | 6.3            | 9.9             | 12.8           |

| 42         | 4000 | 5280            | 2060            | 1270        | 800             | 570                    | .76            | 1.9            | 3.2            | 5.              | 7·             |

|            | 5963 | 4950            | 1900            | 1230        | 790             | 580                    | 1.2            | 3.1            | 4.8            | 7.6             | 10.3           |

|            | 8100 | 6700            | 1400            | 740         | 580             | 420                    | 1.2            | 5.8            | 11.            | 14.             | 19.3           |

| 43         | 4220 | 6260            | 2150            | 1290        | 840             | 590                    | .67            | 2.             | 3.3            | 5.              | 7.2            |

|            | 6290 | 6330            | 1950            | 1260        | 840             | 600                    | .94            | 3.2            | 5.             | 7.5             | 10.4           |

|            | 8386 | 6300            | 2070            | 1300        | 840             | 600                    | 1.3            | 4.1            | 6.4            | 10.             | 14.            |

| <u>ት</u> ት | 4424 | 7070            | 2160            | 1360        | 890             | 610                    | .63            | 2.1            | 3.3            | 5.              | 7.3            |

|            | 6636 | 6875            | 2000            | 1250        | 850             | 640                    | .96            | 3.3            | 5.3            | 7.8             | 10.2           |

|            | 8848 | 6380            | 2000            | 1300        | 820             | 680                    | 1.3            | 4.2            | 6.5            | 10.2            | 12.5           |

| 45         | 4660 | 6450            | 2310            | 1430        | 920             | 670                    | •72            | 2.             | 3.3            | 5.1             | 7.             |

|            | 7090 | 7440            | 2110            | 1350        | 880             | 630                    | •95            | 3.4            | 5.2            | 8.1             | 11.2           |

|            | 9220 | 6970            | 2120            | 1330        | 900             | 650                    | 1•3            | 4.3            | 6.9            | 10.1            | 14.2           |

Figure 1.5.6 Audio Filter Performance Chart

| туре  | Filter | L<br>(hys) | Fc<br>(cps)          | C<br>(μF)              | Rp<br>(a) | R <sub>1</sub><br>(Ω) | R <sub>3</sub><br>(Ω) | R <sub>5</sub><br>(Ω) | <sup>R</sup> 8<br>(Ω) | R <sub>12</sub> |

|-------|--------|------------|----------------------|------------------------|-----------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------|

| MQL-1 | 1      | 10         | 31.6<br>47.5<br>63.2 | 2.53<br>1.12<br>.640   | 29.4      | 2980                  | 910                   | 500                   | 275                   | 148             |

|       | 2      | 10         | 65<br>96<br>128      | .620<br>.275<br>.155   | 81        | 6550                  | 1870                  | 1020                  | 560                   | 303             |

|       | 3      | 10         | 100<br>149<br>200    | .252<br>.112<br>.063   | 103       | 10800                 | 2970                  | 1610                  | 870                   | 470             |

|       | 4      | 10         | 135<br>202<br>270    | .140<br>.063<br>.035   | 164       | 15000                 | 4 <b>1</b> 50         | 2320                  | 1190                  | 640             |

| MQL-0 | 5      | 1          | 173<br>259<br>346    | .840<br>.376<br>.212   | 14.4      | 1620                  | 500                   | 275                   | 150                   | 80              |

|       | 6      | 1          | 212<br>318<br>424    | .560<br>.248<br>.140   | 16.7      | 2010                  | 607                   | 335                   | 183                   | 100             |

|       | 7      | 1          | 254<br>381<br>508    | .392<br>.176<br>.100   | 11        | 2420                  | 730                   | 403                   | 221                   | 120             |

| MQB-6 | 8      | 1          | 297<br>445<br>594    | .288<br>.128<br>.072   | 62.5      | 2850                  | 845                   | 466                   | 256                   | 137             |

|       | 9      | 1          | 343<br>514<br>686    | .216<br>.096<br>.054   | 74        | 3330                  | 935                   | 540                   | 293                   | 162             |

|       | 10     | 1          | 390<br>585<br>780    | .168<br>.074<br>.042   | 87        | 3800                  | 1130                  | 613                   | 337                   | 183             |

|       | 11     | 1          | 439<br>659<br>878    | .131<br>.0584<br>.0328 |           | 4305                  | 1265                  | 705                   | 381                   | 210             |

| Type F | ilter | L<br>(hys) | Fc<br>(cps)                          | С                               | R <sub>p</sub> | R <sub>1</sub> | R <sub>3</sub> | R <sub>5</sub> | R <sub>8</sub> | R <sub>12</sub> |

|--------|-------|------------|--------------------------------------|---------------------------------|----------------|----------------|----------------|----------------|----------------|-----------------|

| MQL-12 | 12    | 1.         | 492<br>745<br>984                    | .105°<br>.0456<br>.0261         | 64             | 4930           | 1440           | 795            | 430            | 234             |

|        | 13    | 1          | 547<br>820<br>1094                   | .0847<br>.0376<br>.0211         | 75             | 5480           | 1592           | 875            | 475            | 258             |

|        | 14    | 1          | 603<br>9 <b>0</b> 5<br>12 <b>0</b> 6 | .0695<br>.0309<br>.0174         | 86             | 6120           | 1770           | 963            | 525            | 284             |

|        | 15    | 1          | 667<br>1000<br>1334                  | .058<br>.0253<br>.0142          | 91             | 6850           | 1945           | 1065           | 573            | 314             |

|        | 16    | 1          | 731<br>1096<br>1462                  | .0475<br>.0211<br>.0119         | 117            | 7585           | 2140           | 1170           | 638            | 345             |

|        | 17    | 1          | 796<br>1194<br>1592                  | .0400<br>.0178<br>.0100         | 140            | 8380           | 2350           | 1280           | 698            | 378             |

|        | 18    | 1          | 866<br>1298<br>1732                  | .0339<br>. <b>0150</b><br>.0085 | 160            | 9235           | 2570           | 1396           | <b>7</b> 59    | 411             |

|        | 19    | 1          | 938<br>14 <b>0</b> 6<br>1876         | .0288<br>.0128<br>.0072         | 184            | 10140          | 2785           | 1513           | 823            | 446             |

|        | 20    | 1          | 1014<br>1520<br>2028                 | .0247<br>.0109<br>.0062         | 208            | 11130          | 3022           | 1640           | 891            | 483             |

|        | 21    | 1          | 1092<br>1638<br>2184                 | .0212<br>.00942<br>.00531       | 232            | 12200          | 3290           | 1770           | 960            | 520             |

|        | 22    | ı          | 1164<br>1746<br>2328                 | .0187<br>.0083<br>.00457        | 254            | 13100          | 3508           | 1890           | 1020           | 555             |

|        | 23    | 1          | 1264<br>1893<br>2524                 | .0158<br>.00687<br>.00397       |                | 14600          | 3830           | 2050           | 1100           | 650             |

| Type          | Filter | L<br>(hys) | Fc (cps)                    | C                         | R <sub>p</sub> | R <sub>1</sub> | R <sub>3</sub> | R <sub>5</sub> | <sup>R</sup> 8 | R <sub>12</sub> |

|---------------|--------|------------|-----------------------------|---------------------------|----------------|----------------|----------------|----------------|----------------|-----------------|

| MQA-9         | 24     | •3         | 1355<br>2032<br>2710        | .0461<br>.0204<br>.0115   | 93             | 3970           | 1130           | 650            | 360            | 200             |

| 0) 1<br>1 0 1 | 25     | •3         | 1450<br>2175<br>2900        | .0401<br>.0178<br>.0100   | 100            | 4270           | 1250           | 690            | 375            | 200             |

|               | 26     | •3         | 1549<br>2324<br>3098        | .0352<br>.0156<br>.0088   | 111            | 4580           | 1340           | 740            | 400            | 215             |

|               | 27     | •3         | 1648<br>2472<br>3296        | .0310<br>.0137<br>.00775  |                | 4900           | 1420           | 785            | 425            | 230             |

|               | 28     | •3         | 1763<br>2645<br>3526        | .0271<br>.0121<br>.00687  | 130            | 5300           | 1520           | 850            | 460            | 250             |

|               | 29     | •3         | 1879<br>2818<br>3758        | .0239<br>.0106<br>.00598  | 138            | 5670           | 1630           | 900            | 490            | 260             |

|               | 30     | •3         | 1998<br>2999<br>3996        | .0211<br>.0094<br>.0053   | 149            | 6100           | 1730           | 960            | 525            | 280             |

|               | 31     | •3         | 2125<br>3187<br>4250        | .0187<br>.0083<br>.00467  | 165            | 6640           | 1910           | 1020           | 560            | 300             |

|               | 32     | •3         | <b>2257</b><br>3385<br>4515 | .0166<br>.00735<br>.00414 |                | 6980           | 1990           | 1080           | 600            | 320             |

|               | 33     | •3         | 2396<br>3594<br>4792        | .0147<br>.00652<br>.00369 |                | 7450           | 2110           | 1150           | 625            | 340             |

|               | 34     | •3         | 2540<br>3810<br>5080        | .0131<br>.00581<br>.00339 |                | 7970           | 2240           | 1220           | 675            | 365             |

|               | 35     | •3         | 2691<br>4037<br>5382        | .0117<br>.00519<br>.00292 | -              | 8600           | 2340           | 1300           | 720            | 390             |

| Type  | Filter | L<br>(hys) | Fc<br>(eps)          | C                          | Rp  | $R_1$ | R <sub>3</sub> | R <sub>5</sub> | R <sub>8</sub> | R <sub>12</sub> |

|-------|--------|------------|----------------------|----------------------------|-----|-------|----------------|----------------|----------------|-----------------|

|       | 36     | •3         | 2857<br>4285<br>5714 | .0103<br>.0046<br>.00259   | 220 | 8950  | 2550           | 1380           | 760            | 410             |

|       | 37     | •3         | 3017<br>4525<br>6034 | .0093<br>.0042<br>.00232   | 235 | 9750  | 2700           | 1460           | 810            | 440             |

|       | 38     | •3         | 3191<br>4787<br>6382 | .00828<br>.00369<br>.00207 | 235 | 10400 | 2850           | 1540           | 850            | 460             |

| MQA-7 | 39     | .12        | 3374<br>5061<br>6748 | .0185<br>.00826<br>.00463  | 98  | 3950  | 1160           | 650            | 350            | 190             |

|       | 40     | .12        | 3564<br>5346<br>7128 | .0165<br>.00739<br>.00415  | 111 | 4200  | 1230           | 690            | 380            | 206             |

|       | 41     | .12        | 3764<br>5646<br>7528 | .0149<br>.00661<br>.00372  | 118 | 4460  | 1310           | 695            | 380            | 203             |

|       | 42     | .12        | 3975<br>5963<br>7950 | .0133<br>.00594<br>.00333  | 117 | 4720  | 1390           | 760            | 414            | 225             |

| ×     | 43     | .12        | 4193<br>6290<br>8386 | .012<br>.00534<br>.003     | 128 | 5000  | 1460           | 800            | 440            | 238             |

|       | 14.14  | .12        | 4424<br>6636<br>8848 | .0108<br>.0047<br>.00269   | 135 | 5325  | 1530           | 850            | 460            | 251             |

|       | 45     | .12        | 4666<br>6999<br>9332 | .00971<br>.00431<br>.00242 | 146 | 5630  | 1633           | 893            | 488            | 265             |

### 1.6 Audio Filter Amplifier

Dwg. No. 4.2.1 Filter Amplifier and Log Converter

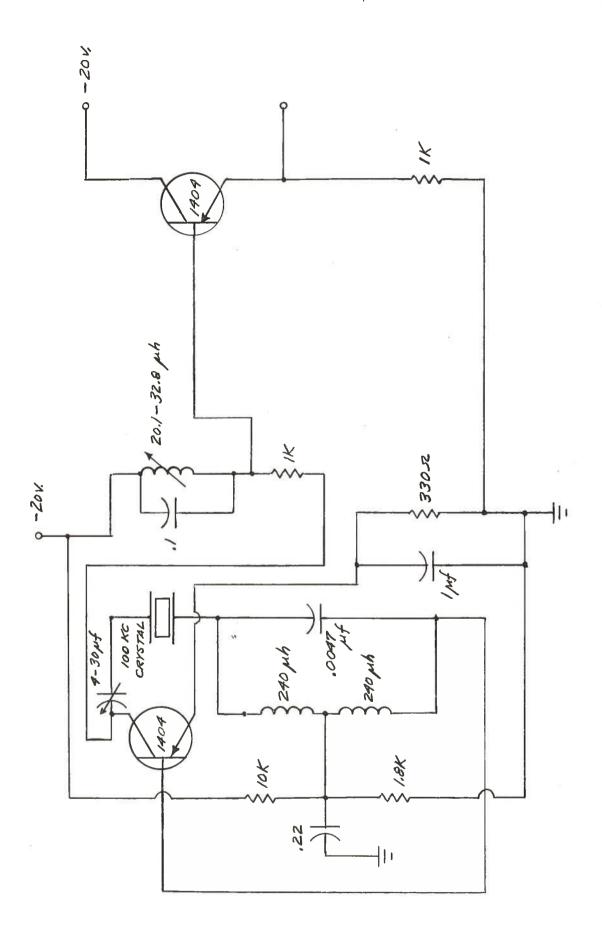

The filter amplifier (fig. 1.6.1) consists of five transistors numbered Q1 through Q5. Q1 and Q2 are cascaded emitter followers providing a high impedance (54KQ) input to the signal from the audio filters (section 1.5). Q3 is a high gain (20 db) class A amplifier feeding into emitter follower Q4, which in turn drives the power output stage Q5. Q5 is also operating under class A conditions, but in order to obtain a flat frequency response (3 dbs down from 30 cps to 15 Kcps) with a low price transformer, it incorporates a feedback loop from the secondary of T1 to the base of Q4.

The output of Tl is rectified by a full wave bridge rectifier, and filtered through CHl, Cll, and Cl2. In order to keep the signal frequency ripple below 5% (5V. at 100V.) choke CHl and filter capacitor Cl2 are required in the twelve low frequency amplifiers. More smoothing would interfere with the speed of response.

A tap between R21 and R22 is available in order to monitor the output of the filters at the control room oscilloscope. At this point the impedance level is fairly low (about  $1000\Omega$ ), so the loading effect of the shielded cable (240K $\Omega$  per foot at 10,000 cps) is negligible.

Gain set R21 should be adjusted to obtain 100 V.D.C. at the input to the log converters (amplifier side of R33) for 100 mv. p.t.p. input to the amplifier.

261

6× 3

-20 V. 1/2 A.

1.7 Logarithmic Converters and Reference Supplies

Dwg. No. 4.2.1 Filter Amplifier and Log Converter

4.2.3 Voltage Regulator Assembly

The log converter (fig. 1.7.1) is a resistor-diode network whose transfer function approximates a logarithmic curve by means of straight line segments. The logarithmic conversion allows the association units to pay attention only to the ratios of the amplitudes of the various frequency components - a very useful form of amplitude normalization.

The particular function to be approximated,  $y = 3 \log_{10} x$ , was chosen because its realization yields practicable voltage and impedance levels. The ideal curve, and the input-output curve of a typical log conversion unit, are shown on figure 1.7.2.

The reference supply voltages represent the y-intercepts of the straight line segments. These voltages are accurately maintained by the log converter voltage regulators at the following values:

V.R. no. 1 at 1.2 Volts V.R. no. 2 at 2.3 Volts V.R. no. 3 at 3.3 Volts V.R. no. 4 at 4.3 Volts

Each of the four log converter regulators is a three transistor circuit, as shown on figure 1.7.3. Q3 is part of the primary feedback loop through R39 and diodes CR8; it acts as a comparison amplifier feeding the cascaded emitter followers Q1 and Q2. R30, R31, and the Zener diode CR7 form the secondary feedback network (the preregulator), and also serve to reduce the ripple current.

Voltage set R39 should not be adjusted to obtain an output more than 20% larger than the nominal value.

A quick check on the frequency channels may be performed as follows: set the input voltage to the audio amplifier at 100 mv p.t.p. Then the input to the log converters should be exactly 100 V, and the output 6 V.D.C.

FIG. 1.7.1: LOGARITHMIC CONVERTER

### 1.8 Plugboard No. 1

Plugboard No. 1 links the outputs of the logarithmic converters to the inputs of the differential amplifiers. Different arrangements on the plugboard correspond to the extraction of different "local" and "global" properties of the frequency-amplitude profile. In general, comparison of the outputs of narrow band filters will yield information about the local features, while the broadband filters and the amplitude monitoring channels will project tonal quality, inflexion pattern, and other global features.

Although the output of each frequency channel is available on eight hubs, no more than four differential amplifiers should be connected to a single one of these channels. The input impedance of the differential amplifier (section 4.5) is of the order of 150 Kohms, and to avoid distortion, the parallel combination of these input impedances should remain small compared to the 15K output impedance of the logarithmic converters.

The logarithmic converters associated with the two amplitude channels have a lower output impedance, and these may be loaded by up to ten differential amplifiers.

The upper row of hubs on the red section of the panel represents the "A" inputs of the differential amplifiers, and the lower row represents the "B" inputs.

### 1.9 Differential Amplifier

Dwg. No. 4.3 Differential Amplifier and Sensory Threshold 10.1 Differential Amplifier (Printed Cct. Leyout)

The differential amplifier amplifying the algebraic difference between the outputs of two logarithmic converters, the  $A_1$ - unit threshold settings, and the gates channelling trigger pulses to the delay chains, are all combined on one card. The circuit is displayed in fig. 1.9.1.

In order to minimize loading on the log units (section 1.7), the input is accepted on either side through a 50 K resistor feeding two transistor cascade direct current emitter followers. The difference amplitude, available between the two emitters, provides the emitter-base bias of two gate transistors used in the ungrounded common base configuration. \* The gate transistors are capacitor coupled through the collector to the Trigger Generator (section 1.11), and through the emitter to the base of the output transistors.

The gates are operated under class A conditions, so that the 1000 cps square wave current through them is proportional to the bias, and hence to the voltage difference between the A input and the B input. Note that one of these transistors is always cut off, depending on whether A is bigger than B, or B bigger than A.

The output transistors are operated in the Class C mode, so that either there is a square wave output big enough to trigger the first multivibrator in the delay chain, or there is no output. The threshold at which each output transistor will fire is independently adjustable on a front panel potentiometer. Thus a certain threshold may be set at which A-B will fire a delay chain, and a different threshold at which B-A will fire another delay chain. The thresholds may be varied to correspond to a filter output amplitude difference of 20% to infinity. The collectors of the output transistors are available on plugboard number 1 (section 1.8).

<sup>\*</sup> This unusual transistor configuration is necessitated by the fact that the output of the double ended difference amplifier is not referenced to ground.

### 1.10 Sensory Delays

Dwg. No. 4.4 Delay Multivibrators and Drivers

10.2 Multivibrator Driver Connections

(Printed Cct. Layout)

4.8 Delay Wiring Diagram - Rack No. 3

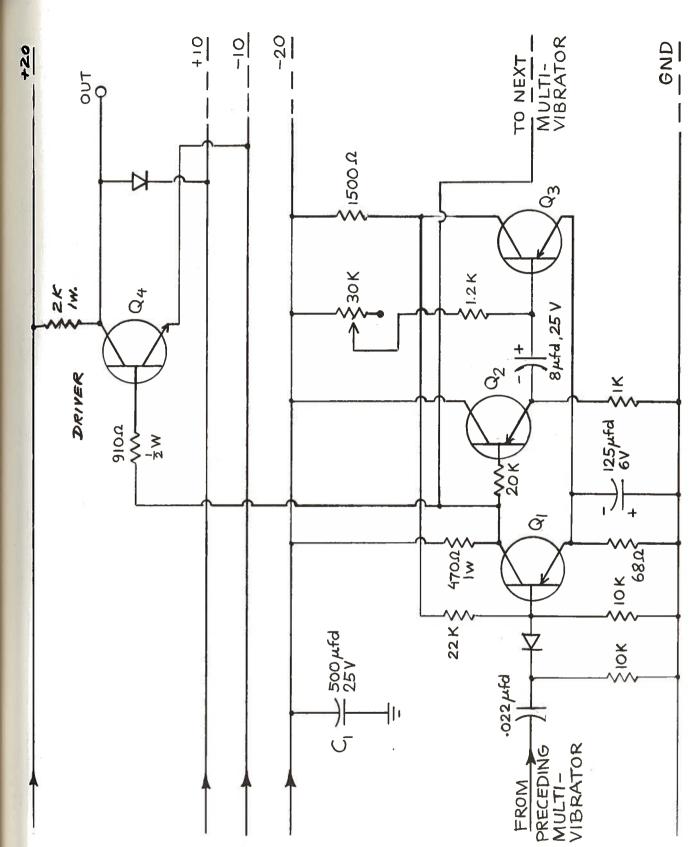

The delay system contains eighty chains of twenty multivibrators each. Each multivibrator consists of a three transistor 'single shot' and a driver (fig. 1.10.1). Whenever the threshold of the differential amplifier (section 1.9) to which a particular delay chain is connected is exceeded, the first 'monoflop' is triggered by the falling edge of the first of the 1000 pps pulses which is passed through the gate. Thus firing is guaranteed within no more than 1 msec. of the time the threshold is exceeded.

The single shots may be set by means of front panel potentiometers to yield delays of about 8 msec to 150 msec each. The recovery time varies between 1 msec and 3 msec depending on the delay settings. The outputs of the drivers (+10V in the quiescent state, -10V in the triggered state) are available at Plugboard No. 2. In addition, the last multivibrator in each chain triggers a lamp driver in the control booth (section 4.5).

Transistors  $Q_1$  and  $Q_2$  in the delay multivibrator are normally off, transistor  $Q_3$  is normally on.  $Q_2$  is just an emitter follower; it is needed to lower the output impedance of  $Q_1$ , for faster recovery time, and to decrease the fall time of the output (this falling edge triggers the next delay in the chain). The delay is approximately equal to  $0.7 \, (R_7 + R_8) \cdot C_3$ . In order that the activity of the delays in a chain may be truly representative of the time dependence of the input, it is necessary to set the delay of the first single shot a little longer than that of the others in the chain. To this end, the first single shot is provided with a 10 fd instead of an 8 fd capacitor.

The delay multivibrators are very sensitive to noise spikes in the power buses, especially in the -20V. line. In order to avoid parasitic triggering, two 500 fd capacitors are hung on each delay board, about half way through the chain.

### 1.11 Trigger Generator

### Dwg. No. 8.3 Trigger Generator

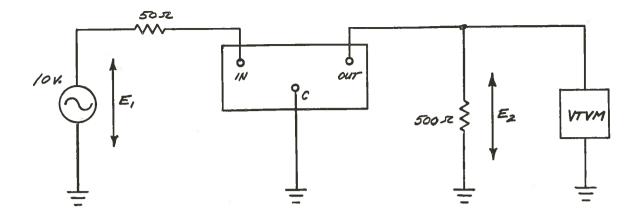

The trigger generator (fig. 1.11.1) provides the sensory delay chains (section 4.6) with negative trigger pulses through the differential amplifiers (section 4.5). Thus the output of the trigger generator is fed simultaneously to all the differential amplifiers, but trigger pulses will be allowed through only to selected multivibrator channels, depending on the direct current input to the differential amplifiers.

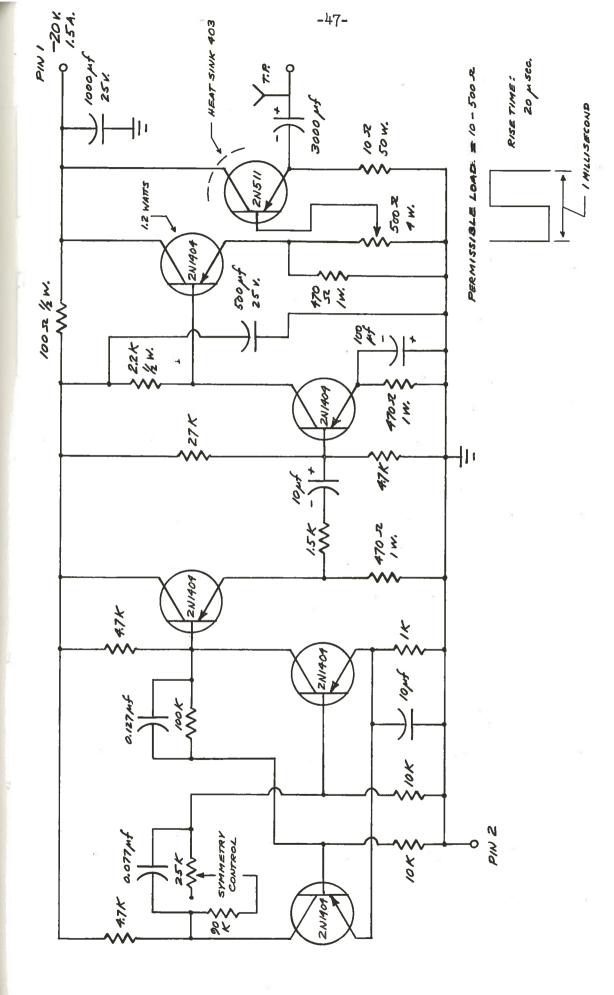

The trigger generator, which shares a chassis with the reinforcement pulse generator (section 3.7), consists of six transistors, numbered Ql through Q6. Ql and Q2 form a 1 Kcs free running multivibrator feeding into emitter follower Q3 and saturated amplifier Q4. Q4 drives emitter follower Q5, whose output amplitude may be varied by R14. Q5, in turn, drives emitter follower power output Q6, which is capable of delivering 1.5 A p.t.p. square wave into a 10 ohm load continuously.

The amplitude adjustment should be set in such a way that, with all the differential pulse gates connected, if the inputs to a test amplifier are balanced, and both thresholds are set to the minimum value, both outputs should be just on the point of triggering the connected multivibrator chains.

### CHAPTER 2 - THE ADAPTIVE SYSTEM

### 2.0 Introduction

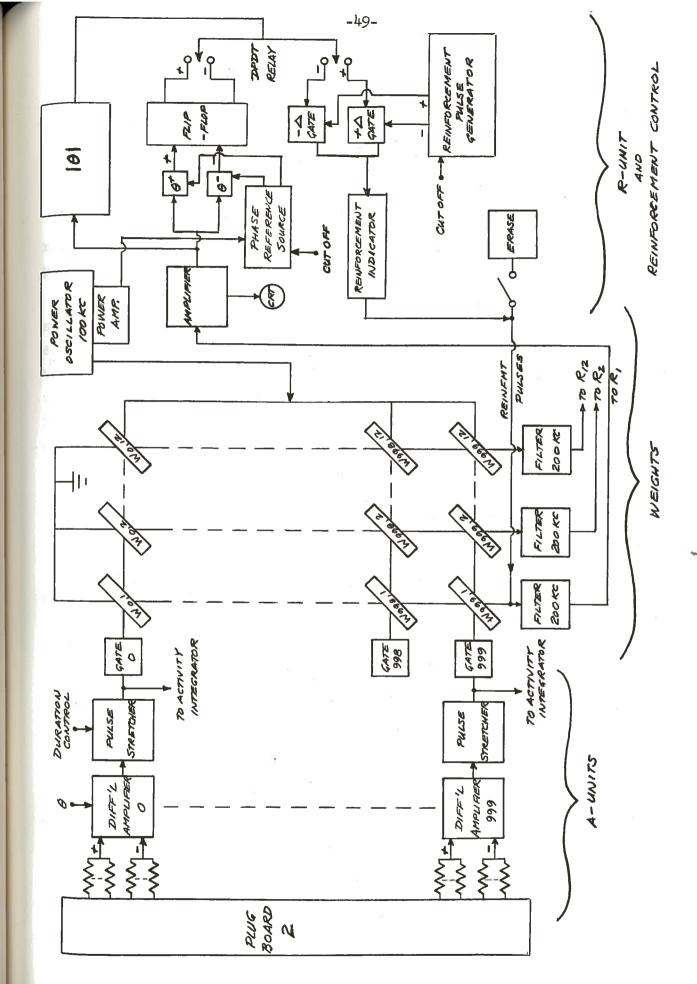

The input to each  $A^{(2)}$  unit (referred to henceforward as the A-unit) may consist of up to twenty delay multivibrator signals. Plugboard no. 1 permits the arbitrary assignment of positive or negative signs to these signals.

The A-unit itself comprises a differential amplifier, an adjustable threshold, a variable pulse stretcher, and a carrier gate (see below). The role of the pulse stretcher is to smooth the sum of input signals to the R-units. The A-unit outputs are accumulated by an activity indicator, which displays the level of A-unit activity throughout a word on the CRT in the control room.

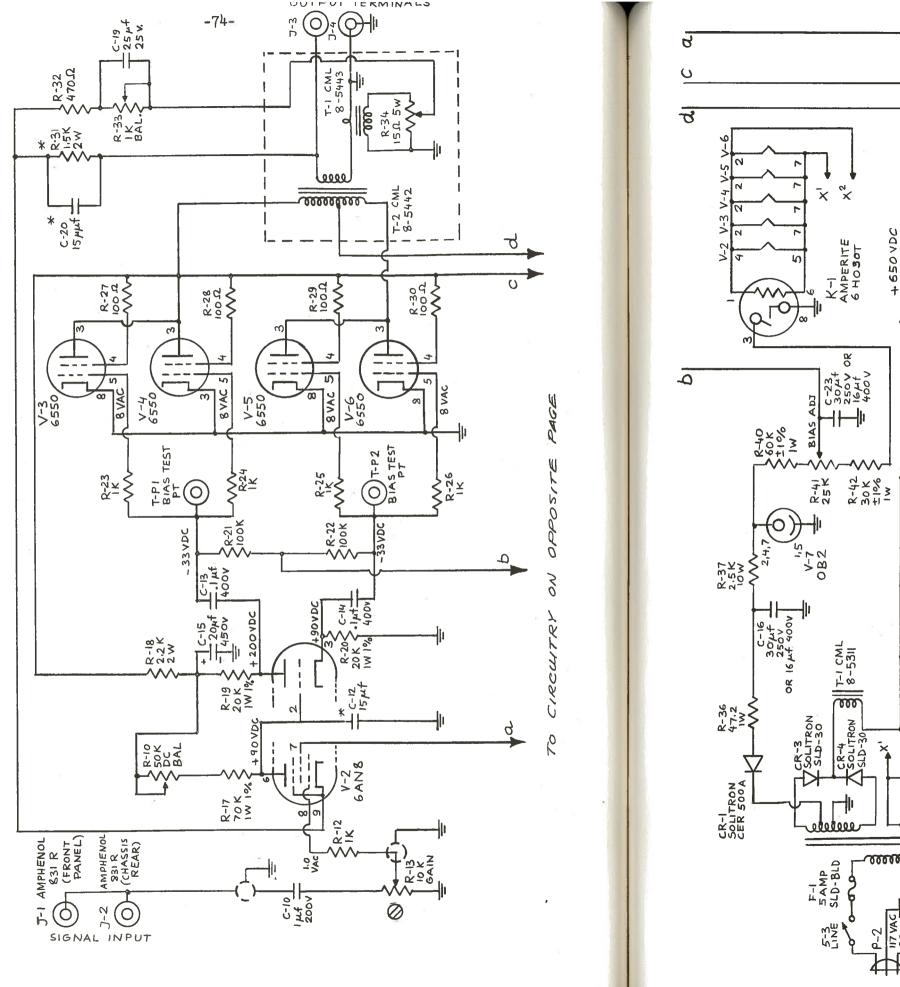

The memory consists of 12,000 tape wound cores, arranged in a 12 by 1000 matrix, as shown in figure 2.0.1. When the threshold of an A-unit is exceeded by the algebraic sum of the signals from the delay multivibrators to which it is connected, it opens a carrier gate, permitting a 100 Kc signal to pass through the drive winding of the twelve cores to which it is connected. The active cores generate a 200 Kc signal (second harmonic) proportional to the stored setting (remanent flux). The algebraic sum (phase reversal denotes sign reversal) of the signal generated in the sense winding (which corresponds to one column of the matrix) is extracted from the carrier fundamental at the R-unit, where it now determines the state of the output flip-flop. The sense winding also serves to increment and decrement the stored flux (by means of pulses), and for erasure.

The R-unit amplifier can be cut off by the response freezing signal from a word termination detector to prevent further changes in the state of the R-unit after an input message has been completed. Precautions are also taken to minimize the effect of noise by ensuring that the R-unit will change its state only if the change in the input is greater than a preset amount. Both the input and output of the R-unit may be monitored in the control room, and the latter is also printed by the automatic typewriter after each word.

Reinforcement is generally performed by an error correction procedure, which requires that the desired response be available in the machine before a word is presented. Depending on the setting of the relay storing the desired response, a "wrong" R-unit will open a positive pulse gate or a negative pulse gate, channelling the appropriate write pulses to the cores associated with it. The reinforcement pulse generator, which provides the necessary write pulses, is turned on only during the period for which reinforcement is permitted, as scheduled by the word termination detector. This period will generally be set for a few milliseconds during which the entire word is "in register", and overlapping the instant at which the response state is frozen. Provision is also made (through the reinforcement overshoot control) to briefly continue reinforcement after the R-unit has reached the correct state, in order to stabilize the correct response.

In summary, the incrementing or decrementing of the flux level of a single core is determined by: 1) the activity state of the A-unit to which its drive winding is connected; 2) the algebraic sum of the inputs to the R-unit to which its sense-write winding is connected; 3) the absolute amplitude of the input to this same R-unit; and 4) the time elapsed since the word has fully entered the delay chains.

### 2.1 Plugboard No. 2

Dwg. No. 5.1 (S-P wiring diagram) Rack and Connector Layout 8.6.5 (P-A wiring diagram) Rack and Connector Layout

The main plugboard (P.B. no. 2 on Dwg. No. 1.2) is mounted on five racks bolted side by side. On the front of each rack there are six 1600 hub panels (black) and five 800 hub panels (black and yellow).

The 1600 hub panels are wired in parallel with each other and with a similar panel at the base of the rear of each rack. Parallel wiring here denotes that corresponding points are wired together. The rear panels are in turn wired in parallel with each other and with a 1600 hub (really two panels totalling 1600 hubs) clip-on terminal block set on the back of rack no. 4. Each of the 1600 terminal block points is connected to the output of one of the sensory delay drivers. Thus the thirty black panels on the plug board represent the same 1600 driver outputs repeated over and over.

The smaller panels represent excitatory (yellow) and inhibitory (black) inputs to the 1000 A-units. Each column of 10 hubs is either the excitatory or the inhibitory input to an A-unit. Isolating resistors (adding resistors in lab parlance) are mounted on the backs of the A-panels. About 1000 of the 20,000 resistors in the plugboard were tested; the resistances were found to average  $19.4 \mathrm{K}\Omega$ , with a standard deviation of  $0.4 \mathrm{K}\Omega$ . The connections to the A-unit racks are wired through multiple plugs and sockets (one set per panel) through overhead cables from the common terminals of the isolating resistor sets.

To establish an S-A connection, one simply selects a free hub in the appropriate black or yellow column, and runs a double male connector to the correct sensory point of the nearest S-panel. The parallel panel organization was devised after consideration of the possibility of extending the chain-wiring method of establishing connections (used in Mark I) to a 1600 x 2000 matrix with up to twenty connections per A-unit and thirty per S-unit. It is expected that the normal connection density will be only a fraction of the permissible density.

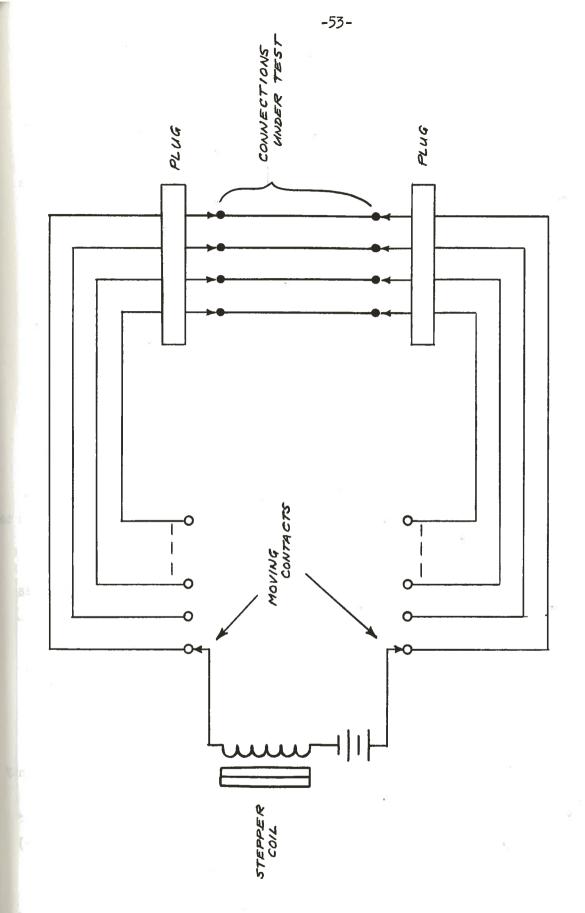

Since there are 48,000 S-point terminations, the probability of wiring errors in the construction of the plug-board is by no means megligible. It is

therefore necessary to test each hub for proper connection to its S-line, i.e. to check whether the corresponding thirty points, and only the corresponding thirty points are connected together.

In general, the most time consuming portion of the testing procedure is the continuity check. An arbitrary panel is chosen, and a continuity check is performed between each hub on that panel, and the corresponding hubs on every other panel. The size of the plug board justified the construction of equipment designed to test several connections simultaneously. A schematic diagram of the S-unit continuity tester is shown on figure 2.1.1.